作者:Kenshin

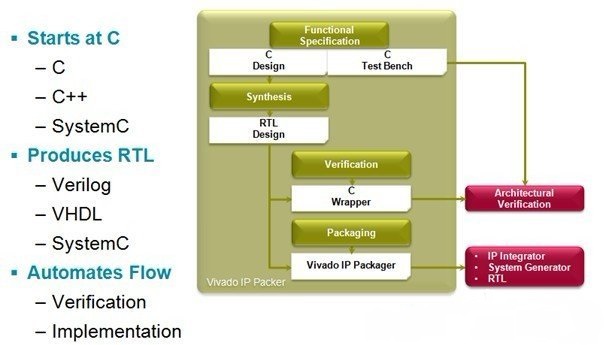

众所周知 Hackaday.com 网站上聚集着众多极客(Geeker),他们打破传统,标新立异,敢于尝试新的东西,今天这篇文章搜集了这些极客对Xilinx Vivado HLS工具使用经验和心得,Xilinx Vivado HLS是一个高级综合工具,能够将C语言转换成硬件描述语言(HDL),也就是说我们可以用C语言来实现HDL模块编程了。

图1 Vivado HLS工作流程

图2 Xilinx赠送给Mike Field的MicroZed开发套件

他总结的步骤如下:

1. HLS工具会将C语言代码转换成伪机器代码,都可以用FPGA逻辑(乘,加,递增等)来实现。

2. 循环操作代码分析,主要是根据语法。不能够被充分执行的循环会导致吞吐量的瓶颈,如果一个复杂的乘运算要花费30个周期,并且你要执行256次那么延迟时间就会介于30和7680周期之间。然而如果你使用原语指令(#pragma HLS_PIPELINE)将其展开256次,那么实现方式就会变成7680级流水线,每个循环还可以接受新的数据。

3. 函数调用可能会引起分离的逻辑实例,支持子函数的创建,也可能引起一系列仲裁接口用于访问单个函数逻辑实例。

4. 对于这些伪机器代码如何连接会生成一个计划时间表,并且会充分考虑到期望的性能约束条件(时钟速度等)。

5. 然后代码生成器会将伪机器代码映射为HDL逻辑逻辑代码(Verilog或VHDL),使用简单的流水线接口来处理参数和和、返回值。其实你还可以添加其它语法或者数据类型来构造AXI协议接口的模块。

6. 最后你就可以将转换后的代码或者IP核添加到传统的HDL工程中。

看起来很简单,其实最重要的是最后我们要进行代码优化,排除bug。我们可以定制很多数据类型(n位的整数,或者固定精度的整数等),灵活的使用这些数据类型,可以帮助我们精简逻辑代码,提升系统设计性能。

图3 基于Vivado HLS生成FIR滤波算法

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网