来源:eettaiwan

美国国防部先进计划署(DARPA)目前正资助开发一种全新的非冯-诺伊曼(non-von-Neumann)架构处理器——称为「分层辨识验证利用」(Hierarchical Identify Verify Exploit;HIVE )。DARPA计划在4年内半内投入8,000万美元,打造这款HIVE处理器。包括英特尔(Intel)与高通(Qualcomm)等芯片商以及国家实验室、大学与国防部承包商North Grumman都加入了这项计划。

美国太平洋西北国家实验室(Pacific Northwest National Laboratory;PNNL)和乔治亚理工学院(Georgia Tech)负责为该处理器打造软件工具,而Northrup Grumman则将建立一座巴尔的摩中心,利用这款号称全世界首款图形分析处理器(GAP)执行国防部(DoD)的图表分析任务。

HIVE使用以数据的多层图形显示作为开始的序列(如图),开启了图解分析处理的方式,在各层之间辨识资数据之间的关系。

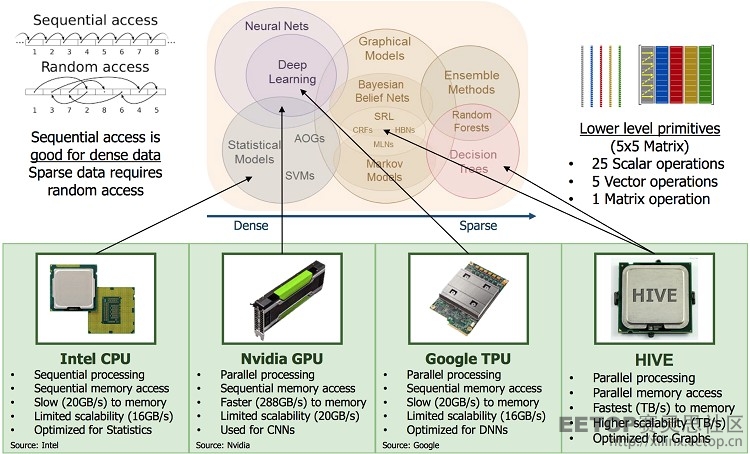

DARPA微系统技术办公室(MTO)计划经理Trung Tran表示:「今天的电脑架构同样采用1940年代发明的[John] von Neumann架构。CPU与GPU均采取平行运算,但它的每个核心仍然是von Neumann处理器。」

Tran说:「HIVE并不是冯诺依曼架构,因为它的数据稀疏,而且能同时在不同的存储区域同时执行不同的过程。这种非冯-诺依曼途径可让许多处理器同时存取,各自采用其本地暂存存储器,在全局存储器上同时执行分散和汇集作业。」

「晶片拼贴图」象征DARPA资助开发的新型处理器计划——「超越微缩:电子复兴计划」(Beyond Scaling: An Electronics Resurgence Initiative)正推动微系统结构和性能的新纪元。

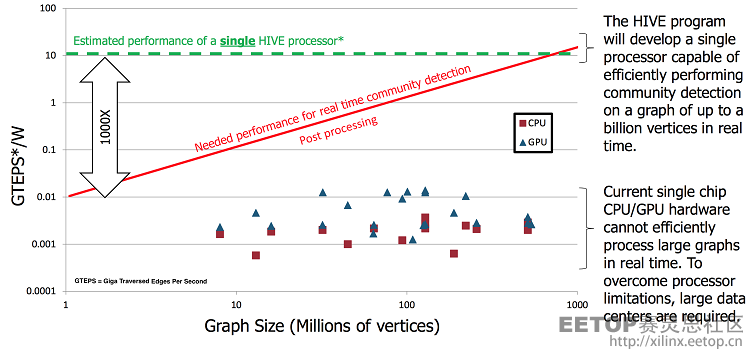

图形分析处理器目前并不存在,但在理论上与CPU和GPU有着显著的不同。首先,它们经最佳化用于处理稀疏图形元素。由于所处理的项目稀疏地位于全局存储器,因而也涉及一种新的存储器架构——能以每秒高达TB容量的超高速度随机存取存储位置。

当今的存储器芯片经过最佳化,能以最高速度存取长序列位置(以填补其快取),这些速度大约落在每秒GB的范围。另一方面,HIVE将以最高速度从全局存储器随机存取8位数据点,然后再以专用的暂存存储器分别处理。该架构据称也具有可扩展能力,但需要许多HIVE处理器执行特定的图形演算法。

Tran说:「当今所收集的所有数据中,只有大约20%是有用的——这就是为什么稀疏——让我们的8位元组粒度对于巨量数据(Big Data)的问题效率更高。」

即时绘图分析需要高达Giga TEPS的处理速度(绿色),才能辨识现场呈现的关系,这较目前速度最快的GPU (蓝色)或CPU (红色)速度更快1,000倍。

这种图形分析处理器采用最佳化的新式演算法处理单元(APU),加上DARPA提供的新存储器架构芯片,据称其功耗较今日的超级电脑功耗更低1,000倍。参与这项计划的组织,特别是英特尔与高通,也将有权商用化这款处理器与存储架构。

根据DARPA,图形分析处理器可用于解决Big Data的问题,因为这方面的问题通常是多对多的关系,而非为目前的处理器最佳化的多对一或一对一的关系。

Tran说:「从我的立场来看,下一个需要解决的大问题就是Big Data,目前采用的方法是回归分析,但对于非常稀疏的数据点之间的关系来说,这种方法是无效的。我们发现,CPU与GPU在处理问题的大小与结果的丰富性之间留下了很大的差距,而图形理论则完美契合目前所看到的这一新兴市场。」

除了HIVE芯片,DARPA也呼吁共同开发软件工具,并藉由同步平行存取随机存储器位置,协助编程这种超越今日平行处理典范的新架构。如果成功了,DARPA宣称这种图形分析处理器将有能力辨识传统CPU与GPU难以处理的许多情况类型。

英特尔CPU、Nvidia GPU、Google TPU和DARPA提出的HIVE处理器之间的应用(上)和性能(下)比较。

DARPA认为,Big Data为图形节点提供了感测器馈送、经济指标、科学和环境测量,而图形的边缘则是不同节点之间的关系,例如亚马逊(Amazon)案例中的「购买」行为。

图形理论分析的基础可以追溯到著名的哲学家Gottfried Wilhelm Leibniz,以及Leonhard Euler在1736年出版的首篇相关论文:「柯尼斯堡七桥问题」(Seven Bridges of Königsberg)。从那时起,图形理论已经发展成为建模随机数据点之间关系的一系列演算法和数学结构。HIVE架构的设计就在于使用这些图形分析来辨识威胁、追踪疾病爆发,以及解答Big Data的问题,因为这些问题寺于目前的传统CPU和GPU来说相当棘手。

为期四年半的DARPA计划在第一年将与英特尔和高通共同设计芯片架构,而Georgia Tech和PNNL则负责开发软件工具。在第一年之后,将会选出一款硬件设计和一款软件工具。DARPA将为赢得硬件设计的公司提供5,000万美元的赞助,但该公司也将自行提供5,000万美元。此外,DARPA还将为赢得软件设计的组织提供700万美元的赞助。

同时,Northrup将获得1,100万美元的资金,用于打造巴尔的摩中心,调查国防部对于图形分析的所有需求,并确保硬件和软件制造商满足这些需求。

英特尔数据中心副总裁Dhiraj Mallick表示:「HIVE计划目的在于针对数据处理,利用图形分析处理器发挥机器学习以及其他人工智慧(AI)的影响力。」

Mallick有信心英特尔的芯片设计将会赢过高通,他说:「英特尔已被要求在这项计划结束时提供16节点的平台,在一块电路板上使用16个HIVE处理器,英特尔也将拥有为全球市场提供产品的权利。」

随着这项计划进展,这款HIVE处理器将可实现即时辨识与感知策略资产。相形之下,Mallick说,至今我们还得依靠「失马锁廄,为时已晚」的事后分析…

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网