Vivado和ISE相比ChipScope已经大幅改变,很多人都不习惯。在ISE中称为ChipScope而Vivado中就称为in system debug。下面就介绍Vivado中如何使用debug工具。

Debug分为3个阶段:

1. 探测信号:在设计中标志想要查看的信号

2. 布局布线:给包含了debug IP的设计布局布线

3. 分析:上板看信号

一 探测信号

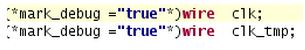

探测信号有2种方法一种是直接在HDL源代码中用(*mark_debug = “true”*)标识出要探测的信号 另一种是 在综合过后的网表文件中添加标志。

1 .在HDL源代码中添加标志

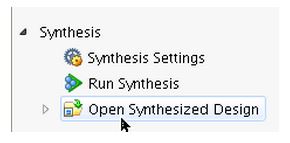

然后点击open Synthesized Design

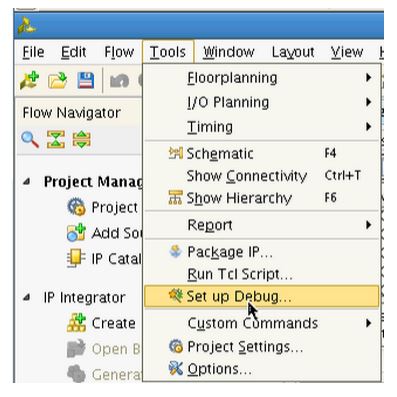

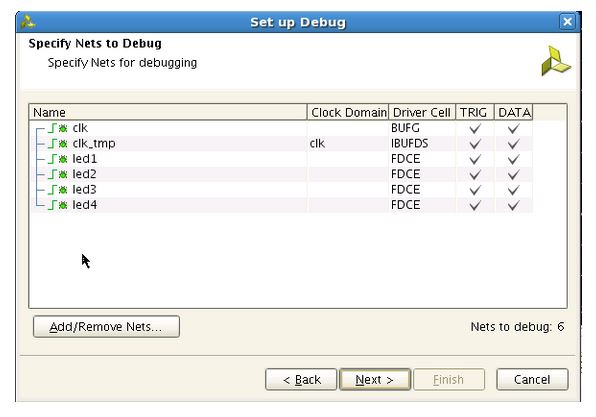

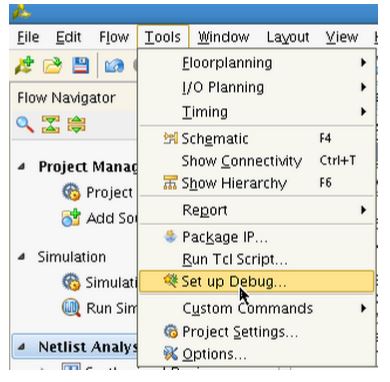

然后点击Tools-> Set Up Debug

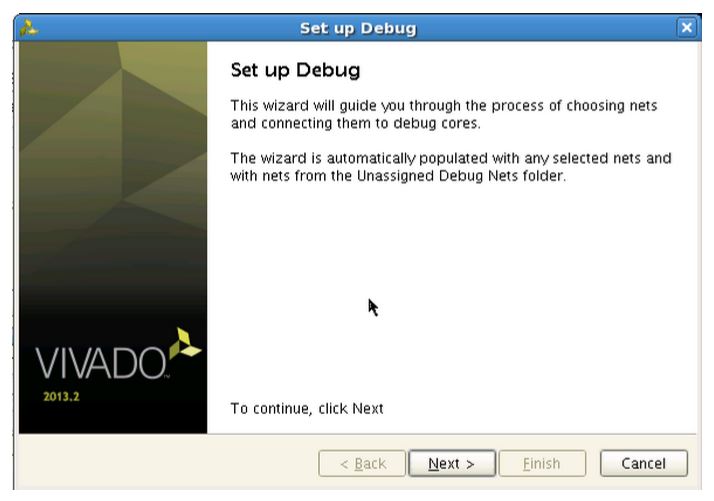

点击 Next

点击Add/Remove Nets

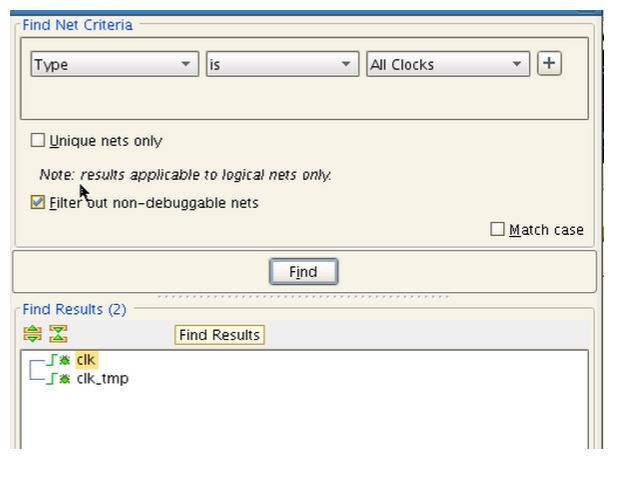

点击find会出来所有信号。如果需要添加debug的信号,从左边框中选择所需信号,点击 按 钮加到右边来。如果需要去除不需要的debug信号,从右边框中选择所需信号,点击

按 钮加到右边来。如果需要去除不需要的debug信号,从右边框中选择所需信号,点击 按钮就 去除了。选好信号之后,在右下角点击Ok按钮。

按钮就 去除了。选好信号之后,在右下角点击Ok按钮。

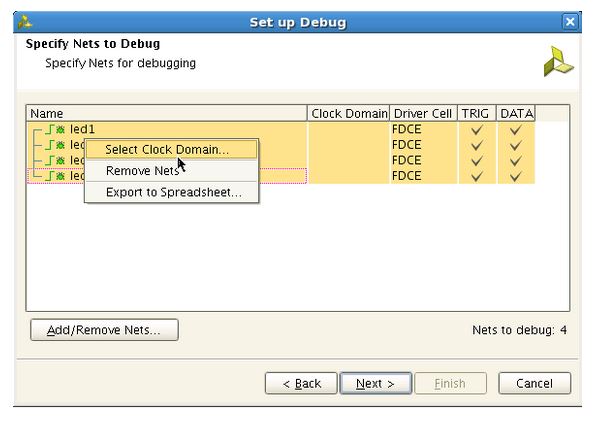

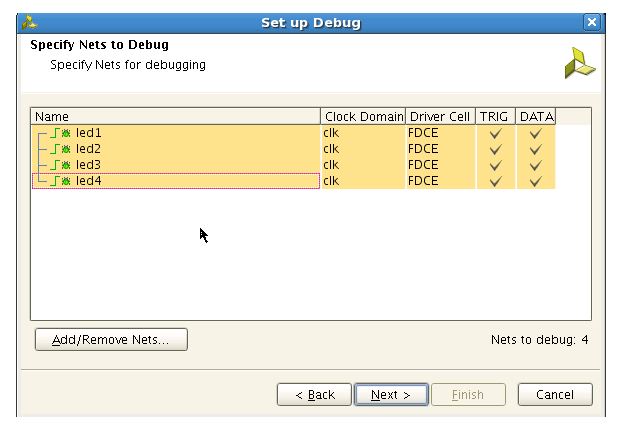

在此框中为所有debug信号选择时钟域,选择debug信号,右键选择Select Clock Domain。注意每一个时钟域对应一个单独的ILA 2.0core。

在此框中选择所需时钟,点击ok

点击next

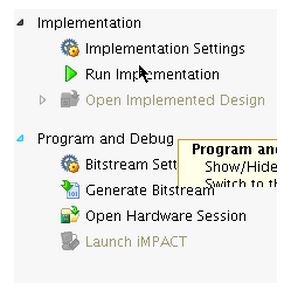

然后继续下面的Implement 流程

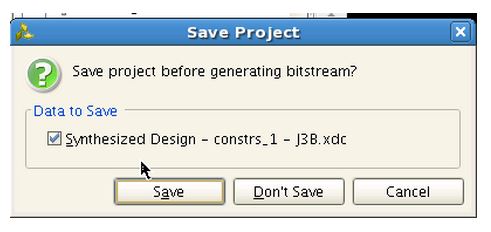

点击Save保存修改后的工程

2.在网表文件中添加标志

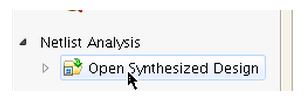

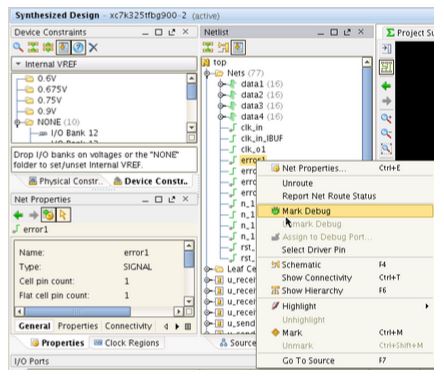

网表文件添加标志,第一步也是打开综合后设计。如下图所示

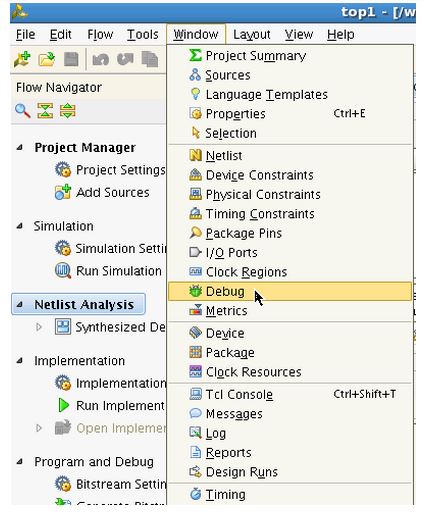

第二步是打开debug窗口

(1) 第一种方法是在Netlist窗口中选择信号,右键点击Mark Debug

(2) 第二种方法是在Tools中选择Setup Debug 推荐使用此方法

二 上板调试

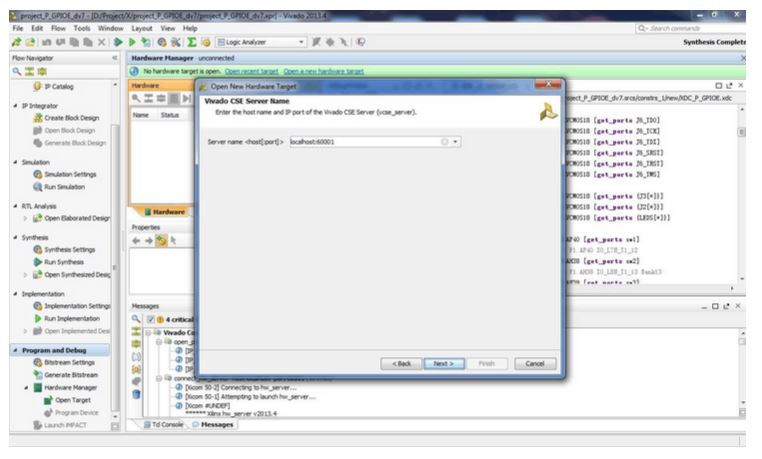

上板的时候选择Open hardware session ,然后Open a new hardware target

选择next

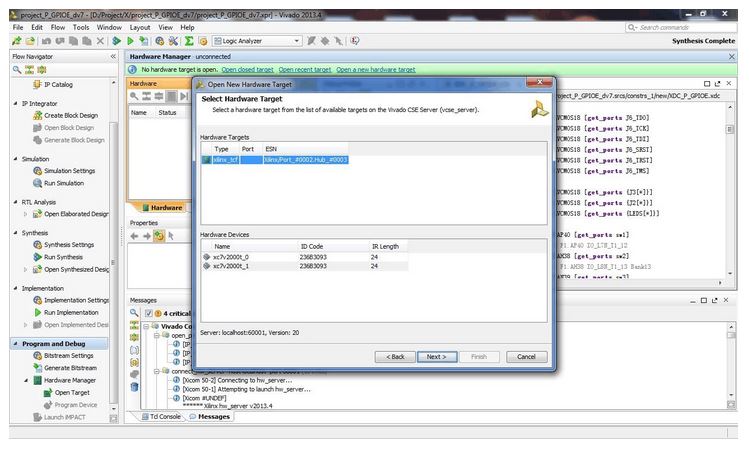

选择next

选择Next

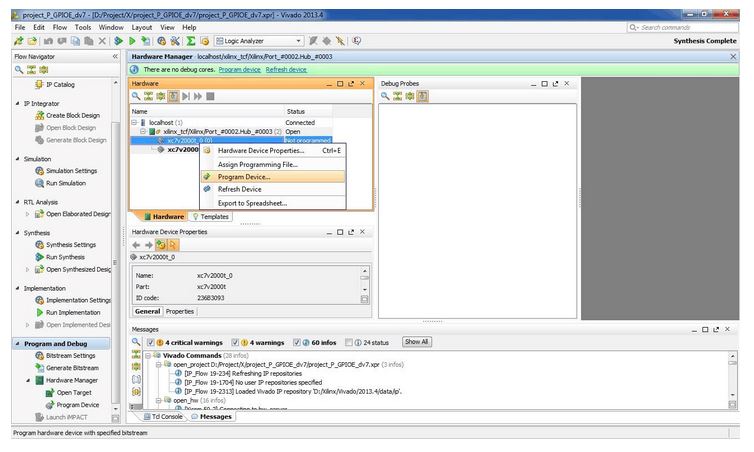

选择FPGA来配置文件

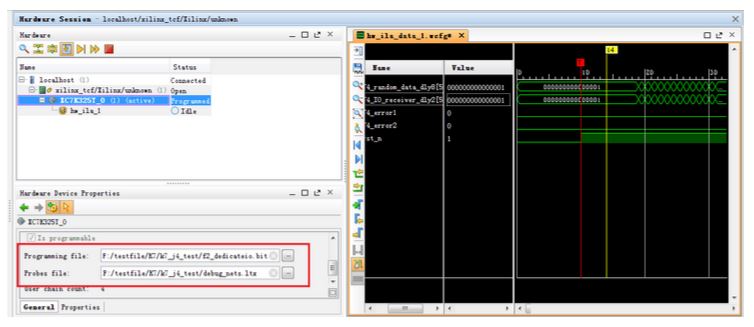

注意移到另一台电脑看debug信号时,必须将debug_nets.ltx 文件和bit文件一起移过去。如下图红框所示

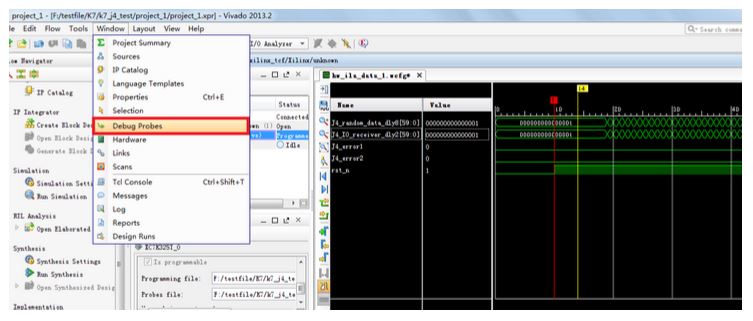

如果需要设置触发条件,选择Windows –> Debug Probes

在Debug Probe窗口中选择需要设置的信号,然后设置触发条件。在Trigger Pos中可以设置抓取到触发信号跳变前N个时钟周期可以被抓到

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网