前言:对FPGA的板极调试,对于大部分的工程师都是一个比较麻烦的事。这样子的事情在开发的初期阶段尤其突显。我就常常有这样子的困扰,比如说,对于一个SDRAM,我希望从我的PC发送一个指令,可以使得FPGA对SDRAM进行写操作或者读操作,对于我还不是很熟悉的芯片,虽然我拿到硬件,也熟读了数据手册,但我还是希望可以实时配置它,验证它的功能。就这样子,趁着这个机会设计与验证了基于RS232的wishbone控制器。

对于PC与FPGA的通信,首先想到的当然是RS232了,即使说它的速度跟性能无法都跟其它的通信方式相比,但是,有两点让我们无法舍弃它:简单、稳定。LX9 Microboard上边的USB-UART更是使得RS232摆脱了DB9这样庞大的接口器件以及使你不需要到处去找串口连接线,毕竟现在来说,找一个串口线比找一个USB线要困难n倍。对于FPGA内部总线,我当然是选择了wishbone总线,相关的总线协议,可以参考资料:Combining WISHBONE interface signals.pdf 百度之即可。推荐中文介绍网页:

http://www.shangshuwu.cn/index.php/OpenRisc_CPU%E7%9A%84Wishbone%E7%89%87%E4%B8%8A%E6%80%BB%E7%BA%BF

最推荐的方式当然是:www.opencores.org 了。

一、控制器设计框图:

二、发送接收方式

其中,每次发送数据之前,发送几个数据,表明是wishbone总线,我采用的方式是:

当数据八位八位的接受了之后,使用状态机提取地址以及数据即可。

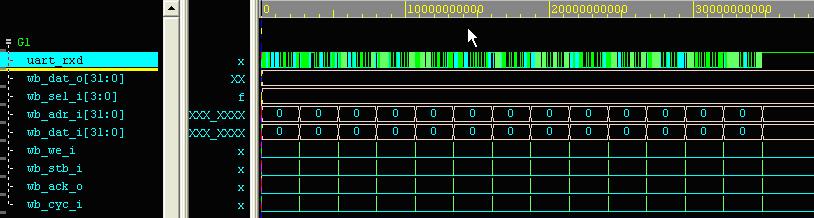

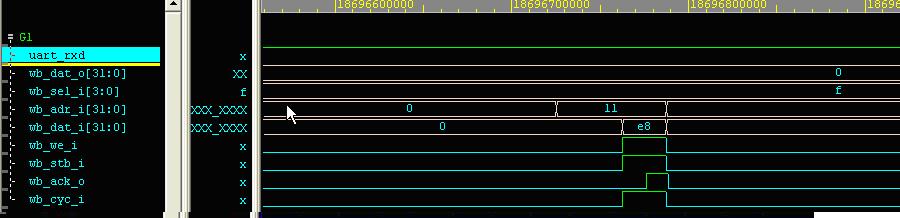

三、仿真

仿真图如下:使用uart的model往设计模块写入地址以及数据

32'h0001_0108 , 32'h0000_0041

32'h0001_01ff , 32'h0000_0001

32'h0001_0109 , 32'h0000_00d1

32'h0001_0103 , 32'h0000_0006

32'h0001_0109 , 32'h0000_00c0

32'h0000_0010 , 32'h0000_000E

32'h0000_0011 , 32'h0000_00E8

32'h0000_0012 , 32'h0000_00A8

32'h0000_0013 , 32'h0000_00C8

32'h0000_0014 , 32'h0000_00C6

32'h0000_0015 , 32'h0000_0005

32'h0000_0016 , 32'h0000_00c2

32'h0000_0017 , 32'h0000_0002

因为时间仓促,接收模块还没有怎么写好,只是实现了从RS232到wishbone总线单向。

四、板极功能验证:

首先,当然要调通串口啦。安装USB-UART驱动以及下载驱动,这个直接看开发板资料就可以了,写的非常清楚明了。串口测试是否正常,我是是使用了我很久以前写的两个个VHDL文件,只有直接发送模块,这些模块,在网络上应该到处都是。然后分别在电脑串口软件以及chipscope上观察数据是否正确即可,这个大家应该都蛮熟的了。

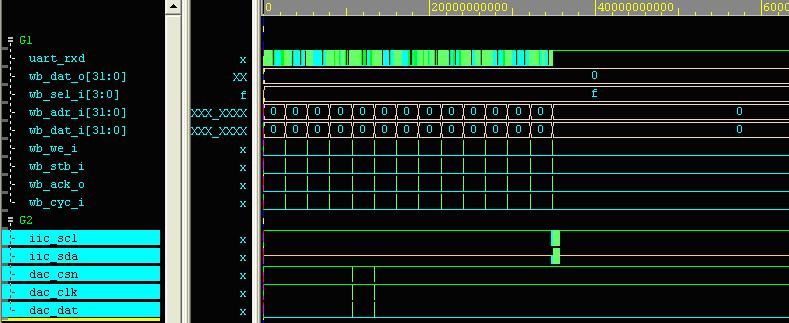

然后,把自己曾经用到的IP放进去。为了方便使用示波器观察数据,我把一个I2C模块以及一个SPI配置的DAC ( TLV5626 )的模块放进去,然后输出到保留引脚上。

下面是应用仿真

建立工程以及综合下载那些琐碎事,就不在这里多扯了。

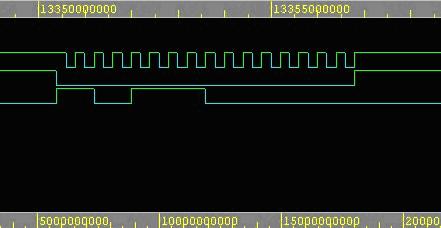

结果验证:

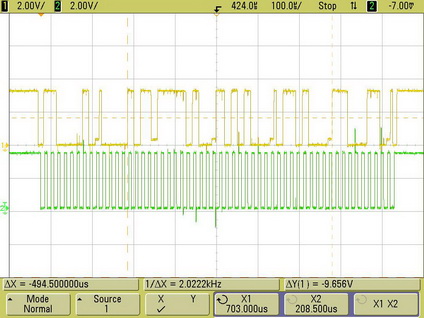

下面是示波器观察I2C的结果:

可以对比仿真结果与示波器的观察结果,是一致的。

总结:最近忙的东西比较多,时间也比较有限,自己对嵌入式那一块也不是很熟,所以感觉没办怎么用到这个板子比较高级的地方,其实,如果可以做一个网口控制器的话,那就相当的high了。

DB

2011.8.24

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网