作者:单连福 EETOP ID: shiyinjita

前言

单纯的FPGA逻辑在并行性上有很大的优势,而在串行执行,尤其是要初始化几十步并且每一步在执行多个周期上面,就会显的严重不方便,而利用EDK这样就会方便很多,

因此本文的计划是在LX9上实现EDK + 逻辑的通信 。

目的 :

在LX9开发板上练习EDK功能,同时把EDK结合到纯逻辑单元中,基于这个目的我选择了8051的IP核 + LAN(EDK实现)。以前我做的一个项目用用单纯的逻辑实现网口竟然占用了500个查找表,所以想来尝试用EDK实现。

工具与器材

1 :LX9开发板

2: ISE12.4 ;

3,示波器(泰克)

4:网上下载的英文文献

5:8051的IP核。

方案:

1:网口采用EDK实现,通过网络传输 :

2:在8051上面实现一个对数运算的IP核心 。

3:网络传输后的数据进入8051的对数运算模块后,通过网络返回。

模块实现 :

1: 对数运算

对数运算有两种实现方式,

1为 展开公式进行运算,这个方案我尝试了10多天也没有实现,最后不得已放弃

2:为查找表实现,这种方案很简单,就是把数据用CASE实现,但是这种方案只能实现少量的数据,比如0-255 ,但是65536个数据的话这样就不可能用FPGA实现了,这样会太浪费资源,

现在有个疑问是如果实现65536个数据的对数运算,大家谁有好方法呢!可以共享一下吗?

2 : 8051的IP核阅读并且把对数的IP核加入到8051中

从网上下载8051的IP核,现在有多种版本,比如(MC8051,R8051,DW8051)

其中最常用,网上资源最多的就是MC8051,这个与INTEL刚开始的8051是基本相同的,缺点也是12个周期,速度上有些限制 。而DW8051我觉得问题在存储这块上,具体代码我来没有来得及细看,R8051是商业上应用的51核,一般是收费的,不过性能很好。

从以上3个版本中选择一个8051的IP核,然后阅读8051IP核。

8051的基本结构为下图所示 :

由于篇幅的限制我就不说每一部分是怎么实现的了,大家有兴趣的话可以看一下8051的书籍以及8051的IP核 :

看完了8051的IP核后,就要考虑怎么加对数运算的IP核了

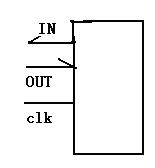

对于把对数的IP核加入到8051的IP核中,下面为对数运算的IP核 :

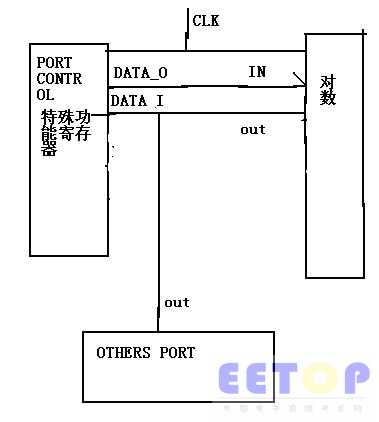

两者组成一个系统如图所示 :

通过特殊功能寄寸器进行控制,

这一步骤仿真并且通过

3 : 通过EDK进行网口控制,

当完成上面两步的时候,已经8。20号了,然后匆匆忙忙的进行EDK的操作,因为以前从来没有EDK,所以这一步遇到了很多问题,而且中间出去了3天就没有时间调试,因此只用EDK实现了一个简单的跑马灯,没有实现网口功能!在这里表示歉意,

4 : 由于没有完成第3步,因此下一步的计划是专攻EDK,争取在年底完全完成!

总结 :

一个月的实验,实验没有完成,这很抱歉!!!!!

不过对于SP6这款有了基本的了解,同时对EDK也有了初步的涉猎,

下一步的计划为继续研究EDK,同时对8051的IP核进行深入研究,

Shiyinjita

20110829

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网