赛灵思“安富利杯”LX9开发板使用征文--通过以太网接口实现ICE调试功能

发布者:jackzhang

时间:2011-08-29 15:29:01

1. 简介我们在SOC设计中,经常用到JTAG以实现scan-chain 扫描, 还可以实现对SOC每个block的RAM、Memory以及每个IP block的寄存器实现读写操作。由于实现JTAG调试,PCB需要10根线的接口连接,于是有的SOC 是以USB转JTAG实现在线调试功能,这样可以减少PCB板子上的BOM及空间,节省设计成本,由于USB的缺陷性,只能在电脑面前调试,不能远程登录,或远程调试。因此本文介绍一种更为新进的在现调试功能。ETHERNET转JTAG, 这样可以实现远程程序升级,远程程序调试。在线调试的更新,可以节省员工的出差费用, 更节省大量的出差调试时间。因此ETHERNET转JTAG调试功能就显得非常必要性与新进性。

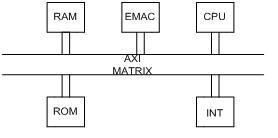

2. 系统构架基于LX9开发板的现有条件, 采用gate counter比较小的CPU,因为CPU连接总线的接口是AXI的接口, 因此总线采用BUS MATRIX协议。以太网的物理端只有100Mbps, 所以我们采用带AXI接口的EMAC IP。并且采用了带AXI接口的interrupter 模块。这样系统就可以初步搭成, 如图1所示,中间是AXI Matrix支持3个master,6个slaver。

图表 1 系统构架

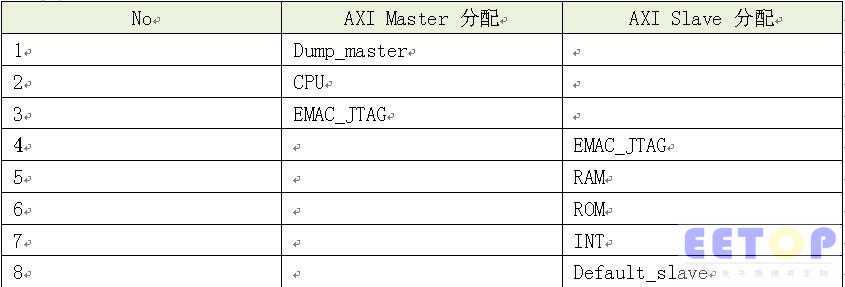

图表 1 系统构架 根据图表1,我们分配各个AXI Master、AXI Slave如图表2所示

图表 2 主从AXI元素分配

图表 2 主从AXI元素分配在确定好主AXI元素,现在需要确定主AXI元素的优先级,如图表3所示Dump_AXI 具有最高优先级,DMA最低优先级,优先级次序由图表3中的数序号确定。

图表 3 主AXI元素优先级分配

图表 3 主AXI元素优先级分配确定好主AXI元素的优先级后,我们现在需要确定每个从AXI模块所占用的地址空间。每个主AXI元素可以访问的几个从AXI元素。如图表4所示,其确定了每个主AXI元素可以访问的从AXI元素的个数。

图表 4 主AXI元素访问从AXI元素的分配

当主从元素的个数分别已确定, 现在可以确定从元素的地址空间。

图表 5从AXI元素的地址分配

3. ETHERNET转JTAG的实现3.1. 总体构架从图表6可以看出, 以太网转JTAG的功能结构中主要包含,以太网的协议控制部分, MII接口的控制部分,JTAG接口控制部分。

图表 6以太网的整体构架

由于AXI总线是在66.6Mhz, 而以太网协议控制部分逻辑主要跑在12.5Mhz 或 1.25Mhz。所以AXI总线与以太网之间用二个FIFO做速度转换,一个给接收用,一个给发送用。 我们初步用每个FIFO深度是72*2, 宽度是8-bit的DPRAM做FIFO。每个FIFO用乒乓协议做数据传递,这样保证速度一直可以工作状态。在接收数据时,处理顺序为:

1> ARM一直check FIFO的half_emp为1或full_emp=1。当half_emp为1时,ARM搬运数据到FIFO里, 当地址从0增加到63时, 设half_tx_valid为1;当full_emp为1时,ARM搬运数据到FIFO里, 当地址从64增加到127时, 设full_tx_valid为1。

2> 以太网检测half_tx_valid或full_tx_valid为1时, 先将相应的half_emp或full_emp置0,然后开始从相应的位置搬运数据,给JTAG处理,当数据被JTAG处理完,才将相应的half_emp或full_emp置1。

在送数据时,也是根据上面的处理协议。

由于本系统主要是实现基于以太网的JTAG,所以主要考虑以太网的功能实现以及JTAG的功能实现。其它的功能会在今后的时间里以完善跟改进。

3.2. 以太网实现由于LX9只支持100Mhz的数据速率,所以我们采用的接口是MII, 这个接口有关的协议请参考802.3标准.

3.2.1. MII接口定义而在定义接口连接线时,初步选定图表7中的接口定义,以便实现起来方便。

图表 7 MII 接口定义

3.2.2. Frame 格式根据802.3的包格式要起,最小包里的数据BYTE是72个,小于72的,需要在数据项里加0。

图表 8 802.3的数据包定义

图表 8 802.3的数据包定义 3.2.3. 寄存器定义

根据数据帧包的格式,以及可扩展性,我们将DA、SA、Length-type数据用寄存器存放。DA需要6-byte,SA需要6-byte, Length-type需要2-byte,这样共需要14-byte的寄存器

3.2.4. 发送FSM1〉 检测full_valid/half_valid, 如果相应的valid为1,只立即将相关的emp置为0

2〉 发送 preample数据

3〉 发送 SFD数据

4〉 从寄存器中读数据,给JTAG发送

5〉 从AXI总线中的RAM读数据到乒乓FIFO中,JTAG开始工作

6〉 5处理完后,将CRC的数据发送

3.2.5. 接收FSM跟3.2.4类似

3.3. JTAG实现JTAG是遵守IEEE-1149.1(JTAG)port,这个接口有关的协议请参考相关标准.

3.3.1. JTAG接口定义图表 9 JTAG 接口定义

3.3.2. 寄存器定义此处的寄存器主要定义芯片公司的ID、芯片产品的序列、芯片总线的位宽、PC地址、JTAG执行种类命令寄存器。

3.3.3. FSM构架图1〉 检测芯片公司的名称,产品序列,位宽,去决定是否支持此芯片。

2〉 检测本次JTAG要执行的命令种类

3〉 检测执行的PC地址跟寄存器PC的值比较,看是否需要产生中断。