# 赛灵思 FPGA 在便携式超声系统 中的应用

作者: Todd Koelling

人们一直希望便携式超声系统能以低成本提供出色的 分辨率。便携式系统使医疗保健服务提供商能够在灾 区、发展中地区和战场等地区使用超声设备,而此前 这还是不可能的事情。

然而设计这些结构紧凑的系统非常复杂,面临诸多挑战,因为此类系统要包含多达 128 个通道,要求支持连续波多普勒,满足众多连接功能要求,支持模数转换、高端 DSP、高速互联和强大的处理能力等。本白皮书将向设计工程师介绍如何利用 Virtex-6、Spartan-6和 7系列 FPGA 解决上述复杂问题,在适当的成本和功耗约束范围内快速为市场提供尖端超声技术。

<sup>©</sup> Copyright 2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCIe and PCI Express are trademarks of PCI-SIG and used under license. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. All other trademarks are the property of their respective owners. All other trademarks are the property of their respective owners.

### 引言

医疗超声技术是对声纳技术的出色运用,使超声医师能够实时观察人体或动物体内组织结构。超声技术最常用于孕妇孕期检查,观察胎儿发育,此外也广泛用于其他众多疾病的诊断治疗,包括急诊室伤情评估、连续波多普勒血流监控以及局部麻醉指导等。近期,我们还在内窥镜远侧顶圆上安装了超声探头,可以更好地诊断胃肠道情况。随着制造工艺、数字处理技术和模拟技术的发展,超声系统不断扩展应用于新型应用中,而且系统尺寸不断缩小,成本不断降低,为偏远地区的医疗保健服务提供商带来了更大帮助。

## 超声技术

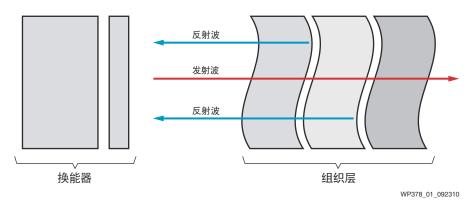

超声设备向身体发射聚焦声束超声波,并通过声波反射的强度及延迟差异重现对象图像,从而形成生物组织的声波照片。声波技术通常配合探头模块末端的压电式换能器阵列使用,按压在身体上。压电式换能器元件在高压(5 V<sub>PP</sub>-300 V<sub>PP</sub>)脉冲电流激励下产生振动,进而生成发射声波。阵列中各个元件的相位彼此对齐,在身体预先指定的位置和距离形成聚焦声束超声波。入射波通过对象时,各组织层之间的声阻抗差就会产生反射发回到换能器(见图 1)。

图 1: 声波反射

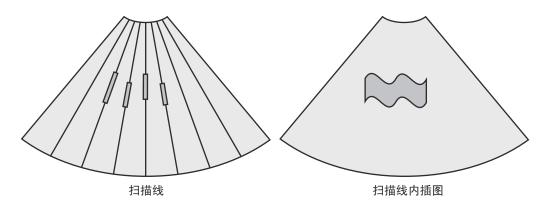

发射声波后,换能器元件立即变成检测器,接受回波信号。在待分析区沿着成百上千条扫描线聚焦发射波束,就能形成代表性身体图,然后在后端电子系统中重组这些扫描线,就形成了 2D 图像(见图 2)。3D 超声系统沿着副轴机械移动换能器阵列,增加三维扫描线。

WP378\_02\_100710

图 2: 通过扫描线形成图像

发射电子器件或发射波束形成器的工作相对简单,只需在图像范围发射声波并正确对 齐相位即可。但接收电子器件的任务则比较复杂,涉及专有技术,要把接收到的声反 射转化为图像。接收电子元件或接收波束形成器必须对各个接收通道适当进行相位对 齐以设置正确的聚焦深度,滤波输入的数据,对波形进行解调,再将所有通道累加在 一起形成扫描线。每条扫描线重复上述操作,然后对所有扫描线进行聚集、内插并滤 波,以形成最终图像。

### 便携式超声系统组件

市场上主要有四种不同外形的便携式超声产品(图3)。

图 3: 便携式超声设备的外形

最小的是手持式超声设备,这是一款手机大小的产品,包括小型显示屏和有限的用户界面,连接到 32 通道或更小的探头。尺寸再大一点的是平板式超声设备,屏幕尺寸适中(约 12 英寸),同时也可用作用户控制的触摸界面。这种系统通常支持 32 至 64 个通道。尺寸再大一些的就是膝上型超声设备,屏幕尺寸通常为 15 英寸,可支持 64 至 196 个通道和连续波多普勒,通常可插入安装槽中,便于使用,还能充电并进行数据传输。第四种类型就是像行李一样最大的"饭盒式"超声设备,其设计类似于膝上型超声设备,但在显示器背后有较大的安装区域,可支持更多功能,有时还能连接更多探头。这种饭盒式超声系统通常支持 64 至 128 个通道。虽然上述所有尺寸超声系统的底层系统架构一样,但所用的组件不同。本白皮书将重点介绍膝上型超声设备。

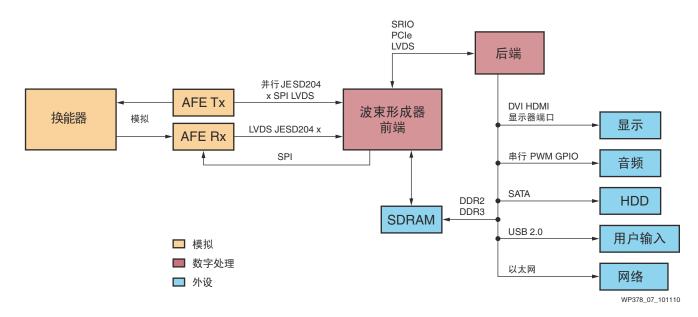

从高级层面而言,超声系统由三个独特的处理模块组成:模拟前端 (AFE)、带前端处理功能的波束形成器和后端(见图 4)。

图 4: 超声系统模块方框图

### 模拟前端 (AFE)

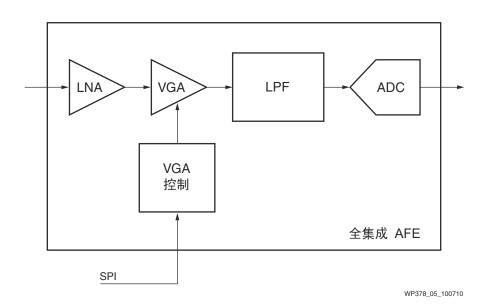

模拟前端 (AFE) 是超声应用中一款高度专业化的系统,既可通过每8至16个通道采用全集成单芯片的形式,也可通过每通道采用多芯片定制解决方案来实现。为了满足换能器接收信号动态范围较大的要求,我们可用可变增益放大器 (VGA)或时间增益补偿器 (TGC) 将信号映射到模数转换器 (ADC) 较窄的动态范围上。在全集成 AFE (图5)中,VGA/TGC 由逻辑通过 SPI 接口控制。而在不采用全集成 AFE 的解决方案中,VGA/TGC 则由模拟波形控制,逻辑通常用来驱动数模转换器 (DAC),以控制可变增益。ADC 数据串行连接,并通过 LVDS 或新兴 JEDEC JESD204x 标准传输到数字处理器件。

图 5: 模拟前端

在 AFE 发射侧,DAC 用来将输出脉冲数据转换为模拟数据。模拟信号驱动高压脉冲器或放大器,进而产生换能器的发射波形。

#### 波束形成器

超声波束形成器包括两个组成部分。发射波束形成器(又称 Tx 波束形成器)负责启动扫描线并生成发送给换能器元件的定时脉冲串,以设置对象所需的聚焦点。接收波束形成器(又称 Rx 波束形成器)负责从模拟前端接收回波波形数据,并将数据通过滤波、开窗(切趾术)、求和及解调整理为代表性扫描线。这两个波束形成器模块保持时间同步,连续向彼此传送时序、位置和控制数据。

Tx 波束形成器负责定时数字脉冲串的导向和生成,该脉冲串外部转换为换能器的高压脉冲。根据给定扫描线聚焦超声波束所需的即时位置可实时计算出延迟。Tx 波束形成器模块相当小,占用的逻辑资源不到 Rx 波束形成器的 10%。其包括时序生成器和脉冲成形,通常并行连接到外部 DAC。

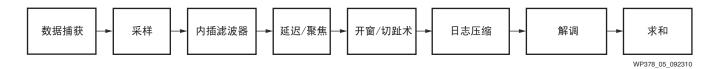

Rx 波束形成器对原始换能器 Rx 数据进行分析,以提取并聚集成超声扫描线。这是一个 DSP 密集型模块,会占用大量的逻辑资源。图 6 对处理步骤和子模块进行了汇总。

图 6: Rx 波束形成器功能步骤

每个通道都要进行上述每个步骤,直到最后求和;而每个扫描线则需要进行其他步骤。这是一种典型的处理流程,实际超声实施方案可采用上述步骤的任意组合,并配合其他专有处理模块。Rx 波束成形可在频域、时域内进行,也可采用其他专有方法执行:

- 数据捕获 对输入的 LVDS 或 JESD204x 数据解串,与时钟同步,并缓冲待处理的数据。

- 采样 对输入的数据过采样,可提高后续延迟过程的精确性。

- 内插滤波器 可进一步扩展和调节延迟不准确性, 从而提高图像精度。

- 延迟/聚焦 每个通道的数据延迟,就焦点相对于每个换能器接收元件的位置进行调节。保持时序同步于 Tx 波束形成器,系统用户能实时修改,从而定向波束和焦点。

- 开窗/切趾术 消除波束响应自然出现的空间图像回声(旁瓣)。

- 求和 对所有通道求和, 生成最终代表性扫描线。

- 解调一解调可从回声载波频率范围中提取最终扫描线。该步骤包括包络检波、下变频、抽取滤波器和匹配滤波器等。希尔波特转换通常用于包络检波。

- 对数压缩 将数据动态范围降至可接受的水平, 以处理和显示图像。

#### 后端处理

后端处理引擎通常包括 B 模、M 模、多普勒和彩色血流处理功能块。上述功能块同时工作,执行多种不同的任务。B 模处理引擎负责接收解调和压缩的扫描线,并用内插和灰度映射在扫描线基础上形成二维灰度图像。M 模将一段时间内的数据点加以比较,从而识别出声源的运动、速度和运动位置。多普勒处理来自多普勒专用模拟前端的数据,并生成精确的方向和速度信息。彩色血流处理模块将色度映射到运动数据上,反映出速度和方向,再将其覆盖到B模功能块生成的灰度图上。随后后端进行清空,根据超声医师和所用显示设备的要求调节图像,并存储、显示和发送静态输出及视频输出。

我们可在超声系统中使用多种不同增强技术来减少斑点,改进聚焦,并设置对比度和灰度深度。例如:

- 角复合 从不同角度比较同一焦点的视图并将这些视图整合为加权和,从而减少斑点,在此过程中要将该数据乘以 2D 矩阵,实现每个角坐标关联。

- 小波分解 用于减少斑点。小波分解可评估信号不同频域,确定是否需要下变频。

- 各向异性双边滤波 用于减少斑点。

- 直方图均衡化 实现对比度和质量均衡的图像。

- 帧平滑 对相邻像素进行平均、调节,从而实现图像平滑。处理过程中采用低通滤 波器。

- 边缘检测 用高通、高提升等锐化滤波器和衍生品消除图像的模糊之处。

上述技术或其他技术也可任意搭配组合,具体取决于系统要求。

## 功耗

降低功耗是一项主要的设计约束。就便携式医疗超声系统而言,降低功耗有几大原因。便携式系统通常采用电池或其他电量有限的电源(如发电机)供电。产品能否成功,在一定程度上取决于电池使用寿命,能不能用有限的电源长时间工作,因此降低功耗至关重要。医疗系统电源对安全性和质量也有着严格的标准要求。在满足上述安全性和质量标准要求的同时,一旦对功率要求有所提升,电源设计必将面临非常严峻的成本和复杂性挑战。

散热也是降低功耗的一大原因。包含大量系统门的半导体以高频时钟控制,会产生极高的热量,必须做好散热工作,确保系统组件的温度在适当的工作范围内。为了实现散热目的,我们必须认真设计散热片、风扇、封装和 PCB。如果便携式超声系统的工作环境温度超过 40°C(104°F),那么我们将面临更加严峻的挑战。热管理系统会增加系统的整体重量、尺寸与成本,风扇速度的提高也会增加功耗。但 FPGA 有助于解决上述一些功耗约束难题。

### 便携式超声系统的接口复杂性

便携式超声系统在小型封装中集成了众多不同类型的组件。每个组件都有不同的接口要求,这就需要我们采用多样化的连接解决方案。然而,随着通道数量的增加,显示屏的大型化以及对更高分辨率图像需求的提高,整个系统带宽需求日益提升,满足不同接口的要求面临越来越严峻的挑战。在多样性和高带宽的双重压力下,对 I/O 数量和组件之间的吞吐量均提出了极高要求。大多数可用的处理器和逻辑器件都不能为传统高速并行接口提供足够的 I/O,也不支持 SATA、USB 和 PCIe® 等必备接口。将设计方案分为多个小型化高引脚数器件且接口采用专用ASSP的传统分区法仅适用于 PCB 面积足够大的系统,而便携式超声系统必须确保小外形,传统方法已不再适用。在此情况下,为解决构建小型化复杂高带宽系统的挑战,出现了一些新的趋势。

便携式超声系统接口存在三大问题。其一,就是波束形成器逻辑和数据转换器之间 AFE 接口的 I/O 数量较多。用于 AFE Rx 电路系统的 ADC 使用的 LVDS 对引脚数量较少,这对超声系统常见的 12 位 50 MSPS ADC 而言是适用的。但就每个通道都有 ADC 的 128 通道系统而言,这就需要 256 个物理 I/O 引脚。在使用 DAC 的 AFE Tx 电路系统中,大多数 100 MSPS 乃至速率更高的 DAC 均采用并行 I/O 来满足较高的带宽要求,即便在 8 位条件下也能支持高带宽。就采用 10 位 DAC 的 128 通道系统而言,除接收侧需要256 个 I/O 引脚之外,还包含超过 1,200 个 I/O。JEDEC JESD204A标准(www.jedec.org)提供了一种比较直接简单的方法,可在数据转换器和逻辑器件之间采用 3.125 Gb/s SerDes 全向点对点链接,从而大幅减少 I/O 数量,简化 PCB 布局,并减少超声系统组件数量。对 ADC 而言,多个通道可使用一个链接,这就能以较少的 I/O 实现更高的带宽。就 DAC 而言,改善非常显著,I/O 数量至少减少了六成。就 ADC或 DAC 给定分辨率和采样率到底需要多少 JESD204A 信道的指南请见:《XAPP876:Virtex-5 FPGA 连接于符合 JESD204A 标准的 ADC》。JESD204A 为未来的超声系统提供了极富吸引力的解决方案。

其二,就是前端和后端处理模块之间的问题。如果系统的数据通道数量低至 64 个,前后端处理要求也会非常高。在单个器件中集成前后端功能块不切实际,且成本也很高。这时我们通常采用多芯片解决方案来满足组件间的高带宽要求。后端所需的组件数通常较少,而前端则需要较多组件,通常是每 8 个通道一个组件。为了尽可能减少I/O 数量,我们通常在两个不同领域之间使用高速 SerDes 链接。在高端系统中(通常为购物车外形),我们可用 PCIe 背板来满足高带宽要求。图 7 给出了现代便携式超声系统中的主要接口。

图 7: 典型便携式超声接口

其三、就是设计人员往往受制于常用组件的成本和 I/O 方面的限制。现在应对便携式超声系统设计复杂性和空间局限性的方法通常是不再采用专用波束形成器 ASIC 或 DSP,而是转而采用 FPGA。虽然 ASIC 在执行所需波束成形功能方面表现非常出色,但 ASIC 生产成本不断提升,除非是真正大批量应用,否则很难承受如此高昂的成本。虽然 DSP 无需像 ASIC 一样进行定制芯片设计,可避免高昂的 NRE 费用,但其支持的接口有限,而且 I/O 数量也有限。此外,DSP 专用于数字处理,因此还需要额外的组件来负责逻辑互联、数据缓冲等。在此情况下,采用 DSP 解决方案所需的系统成本和板级空间都会大大超出设计要求。而 FPGA 则能解决 ASIC 和 DSP 的不足。FPGA 是一种多用途芯片器件,能够让设计人员在单个器件中集成多种系统功能。该器件将一系列可配置存储器、DSP 和 I/O 与大量逻辑单元紧密集成在一起,并采用先进的工艺技术制造而成。单个器件系统集成大幅降低了物理 PCB 级连接的技术挑战和成本压力。

FPGA 不仅仅是一个芯片器件, 更是一个设计平台, 其配套提供设计工具和全面的 IP库, 能帮助用户快速开展设计工作。由于 FPGA 芯片由 FPGA 制造商设计, 因此用户不必担心 NRE 及生产成本。用户只需创建设计, 把设计文件下载到 FPGA 器件上, 就能完成特定设计的配置工作。

### 赛灵思 FPGA 在便携式超声系统中的应用

赛灵思 FPGA 可帮助便携式超声供应商更好地推出小型化高性能低功耗产品。

#### 后端处理

降低功耗的主要原因在于:

- 在电池或发电机供电情况下延长工作时间。

- 减少对电源性能的需求(电源性能受制于严格的质量与安全控制要求)。

- 最大限度地减少系统热量,从而减少散热管理设计的成本、尺寸和重量。

赛灵思 FPGA 能够在以下三个方面进一步降低便携式超声设计的功耗:技术、架构和设计工具。

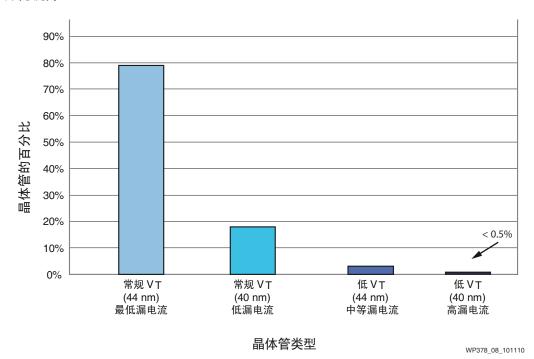

在选择适用于新一代 FPGA 的最新工艺技术节点时,工艺工程师通常面临二选一的情况,一是选择高性能工艺,二是选择低功耗工艺。赛灵思的优先目标是通过各种方法显著降低功耗,同时保持性能方面的领先水平。赛灵思开发出了更加多样化的晶体管,涵盖从超高性能到超低功耗的不同领域,从而实现了上述目标。开发多样性晶体管的优势在于,我们能在整个产品中对晶体管的使用加以战略定位,确保其具有最高的适用性。例如,高速 DSP 模块通过采用高性能晶体管能够确保赛灵思解决方案保持领先的性能水平,而使用漏电流较低的晶体管则能让逻辑阵列大幅降低静态功耗。图 8显示了 Virtex-6 器件的一般晶体管组合。我们对器件中的每个专用模块都进行了精心设计,能够以最低功耗满足所需的性能基准要求。这种方案也在 7 系列 FPGA 中得以延续,而且与前代产品系列和业界竞争型 FPGA 相比,我们利用 28 nm 定制工艺能将静态功耗锐降 40-80%。

图 8: Virtex-6 FPGA 中的 8 种晶体管类型分布

降低功耗不仅限于工艺技术层面,设计和架构团队也要积极协助才能实现赛灵思的功耗目标。通过采用较低功耗的 LUT6 架构,实现更多时钟门控选项以及嵌入 PCI Express、以太网 MAC 等关键 IP 模块,并创建更直接的路由选项,我们能够进一步降低功耗,从而减小连接点之间的电容。A-1L低功耗选项可支持核心 0.9V 电压,相对于1.0V 核心而言能将静态功耗降低 26%,动态功耗降低 20%,而对于需要最小化功耗的应用领域而言,相对于前代 FPGA 而言功耗也能实现 50% 的显著改进。

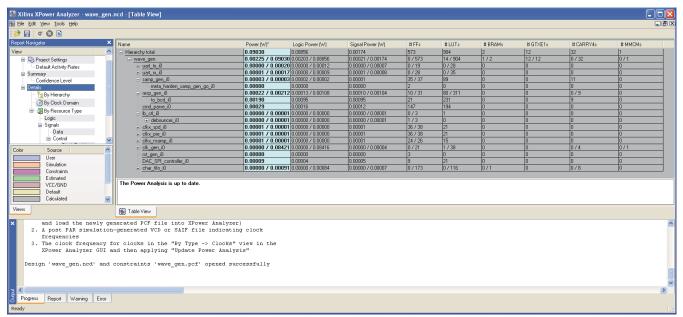

低功耗芯片技术为用户实现静态功耗最小化奠定了坚实的基础,下一步就是在用户的设计中降低动态功耗。赛灵思独特的自动时钟门控技术可提供一系列能自动识别并抵消不必要逻辑活动的算法,而这种活动正是动态功耗的主要成因。仅这一种技术就能将动态功耗降低多达 30%。下一步重要工作就是用赛灵思的 XPower Analyzer 全面分析设计功耗情况,如图 9 所示。

WP378\_09\_101110

图 9: XPower Power 分析界面

该工具可提供准确的实现后功耗分析,凸显了潜在能够降低功耗的设计区域。根据功耗瓶颈情况,用户能够实现赛灵思自动化功耗改进工具的任意组合,如逻辑再综合、功耗优化放置以及路由电容优化等。如果仍需要进一步降低功耗,我们还能用 XPower 工具来明确哪些模块产生的功耗最多,哪些设计方法最适用于降低动态功耗。赛灵思建立了一个可一步步指导客户使用有关工具和功率优化技术的电源技术解决方案 (Power Technology Solutions) 网站,敬请访问网址:

http://www.xilinx.com/products/design resources/power central/

#### 超声优化型 DSP

超声系统中的波束形成器和后端图像处理功能需要极高计算强度的 DSP功能,许多其他采用 FPGA 的应用也一样,这也正是赛灵思为 DSP 架构的设计与优化进行巨大投资的原因所在。Virtex-6 与 Spartan-6 FPGA 采用不同的 DSP 架构。Virtex-6 SXT 器件专为超高性能 DSP 实现低功耗而进行了精心优化,能够支持高达 2,016 个 DSP 宏模块,同时还能实现超过 1,000 GMAC 的 DSP 处理性能。Virtex-6 DSP 架构可在统一的专用 DSP 模块中支持多达 25x18 位乘法器,大幅超越了 12 X 12 位以及 18 X 13 位等常见的超声架构。Spartan-6 LXT FPGA 为低成本 DSP 进行了优化,能以较低成本实现 50 GMAC 的性能水平。7 系列 FPGA 的DSP Slice 可提供支持预加法器和乘法累加器引擎的 25 x 18 动脉元素,能像上代产品一样由相同的控制信号进行控制。此外,其还包含相同的低延迟管道级,并能像 Virtex-6 器件中的 DSP Slice 一样支持模式检测。7 系列 FPGA DSP 采用 28 nm 工艺,能以较低成本和功耗实现更高的性能。

赛灵思可提供广泛系列的高优化度 DSP IP 核。该上述 IP 核使设计人员能够创建器件优化型功能,实现 FPGA DSP 模块的最高性能。常见于超声系统中的一些重要 DSP 功能可充分发挥赛灵思 IP 核的优势,满足高效实现要求:

- 解调功能

- 抽取滤波器 FIR 编译器、CIC 编译器

- 希尔波特转换 FIR 编译器

- 多相滤波器 FIR 编译器

- FFT FFT 内核

- DDS DDS 编译器

- 扫描转换

- CORDIC CORDIC 内核

对于新用户而言,使用 FPGA 取代 DSP 其实非常简单,因为能够支持无需掌握 RTL 设计经验即能实现的高级设计方法。赛灵思推出的 DSP 设计套件配套提供系统生成器 (System Generator) 工具。该软件工具能在 FPGA 设计中使用 MATLAB®/Simulink® 软件建模环境。System Generator 拥有赛灵思精心优化的 100 多个 DSP 构件模块,能够用于快速创建高效率的 DSP 设计方案。此外,这些模块还能从 Simulink 软件模型自动生成并下载 FPGA 编程文件,从而使用户不必再担心 FPGA 实现的细节。

我们能够使用赛灵思的集成型 MATLAB/Simulink 设计流程轻松实现以下功能:

- 切趾

- 海明窗口

- 角度复合

- 小波分解

- 各向异性双边滤波

- 帧平滑

- 边缘检测

第三方高级综合工具供应商还提供其他设计流程选项。这些工具可提供其它设计流程,能满足不同背景和技术水平的开发人员的需求,也能支持传统代码。赛灵思与重要的高级综合工具供应商就认证流程积极展开广泛的合作,可确保为赛灵思客户提供高质量的工作成果,同时简化设计工作的开展。AutoESL 和 Synfora 等公司已经完成了整个认证流程,并为 DSP 开发套件推出了平台支持套件,其中包括特定于赛灵思 DSP的参考设计和辅导资料。

### 采用赛灵思 FPGA 从容应对接口挑战

便携式超声系统中最关键的接口瓶颈是 AFE 到波束形成器的接口,我们在此需要大量 I/O 与并行 DAC 和 LVDS ADC 接口相连。设计工程师很难在不对信号完整性造成任何 影响的情况下确保所有通道上的时序都能精确匹配。《XAPP1071:采用串行 LVDS 接口将 Virtex-6 FPGA 连接至 ADC,用并行 LVDS 接口将 Virtex-6 FPGA 连接至 DAC》对 ADC 和 DAC 接口的设计流程进行介绍了。该应用指南提供了完整的参考设计,同时对具有多种时序波形的每个模块进行阐述,而且还为简化设计人员工作提供了大量指导方案与建议。如欲参阅更多相关应用指南,敬请访问:

http://www.xilinx.com/support/documentation/anbusinterfaceio lvds.htm.

为了进一步降低 AFE 到波束形成器接口的复杂性,模拟供应商采用高速串行JEDEC JESD204A 标准作为从 ADC 向 DAC 传输数据的高效途径,其速率可高达每通道每秒 3.125 Gb。JEDEC 标准采用业界领先的工艺技术,而且 FPGA 厂商与 ASIC 厂商相比也能大幅提前支持高速要求,这就使得 ASIC 往往比 FPGA 落后好几个工艺节点的水平。赛灵思能够为采用 GTP/GTX 收发器的ESD204A 标准提供全方位的支持。《Virtex-5 FPGA 与符合 JESD204A 标准的 ADC 接口相连》(文献号 XAPP876)提供的参考设计将有助于用户在其 FPGA 设计中实现有关接口:

虽然 JESD204A 标准是比较受青睐的解决方案,但并非所有超声模拟前端组件都能为其提供支持。波束形成器 ASIC 可满足并行与 LVDS 接口的某些高级 I/O 要求,但其同时也会造成成本高昂的问题,而这往往是便携式超声系统所无法承受的。此外,单个器件上的大量 I/O 也会导致 ASIC 芯片设计和 PCB 布局面临巨大挑战,从而不仅加大了成本压力,同时也延长了开发时间。更好的解决方案是在多个低逻辑密度的高引脚数 FPGA上对前端设计进行分区。这种方案几乎彻底杜绝了在以下方面同时进行输出(SSO)转换的问题,如:在更多 VCC/GND 对上分布 I/O;为 PCB 布局工程师提供更大的工作面积(这可进一步避免 PCB 路由拥堵问题),以及;为在更大的封装和 PCB 空间(可作为散热片发挥作用)中进行布局设计减少了散热管理问题。不过,设计分区也会带来 PCB 尺寸放大的不利影响,进而导致系统体积增大,因此设计人员应当根据空间约束、通道数量以及模拟前端的设计要求实现良好的平衡。

一些超声系统采用 DSP 来执行波束形成器功能。但是,很少有 DSP 器件能直接与 AFE 组件接口相连并提供所需的解串和数据缓冲功能。在此情况下,FPGA 可谓最佳解决方案,能实现较多的引脚数量,同时还具有大容量的片上存储器。

在便携式超声系统的其他部分,我们可使用各种接口的组合(参阅"便携式超声系统的接口复杂性")。客户既可通过合作伙伴网络获得综合全面的流行 IP 模块组合,也可直接从赛灵思进行订购。除了标准的 IP 核之外,赛灵思还提供 Aurora 简化版接口,以帮助用户设计定制 SerDes 配置并进行精细优化。Aurora 可为物理串行链接提供透明的接口,使专有协议的上层能够方便地使用这些高速串行链接。另外,赛灵思还为Spartan-6 FPGA 上的 SerDes 时序设计提供了应用指南,敬请参阅《XAPP1064:源同步串行和解串(速率高达 1050 Mb/s)》。

#### 可高度扩展的设计

赛灵思 7 系列 FPGA的所有系列产品都采用相同的逻辑架构,从而确保了 IP核的可移植性,使设计人员能够根据不同的平台需要对其设计方案进行上下缩放扩展。设计团队可采用 128 通道的波束成形器 IP 核启动主流平台设计,然后再轻松向下缩调到 64 通道以满足手持或低端平台的需求,当然也可进一步扩展到多达 256 个通道,以支持高级设计需求。由于在 7 系列 FPGA 中,所有器件之间的基本逻辑阵列宏和 DSP 模块都相同,因此经过综合、实例化和低级别时序约束方面实现高度优化的关键设计部分能在最新 7 系列产品的移植中得到保留。这种统一架构能够显著缩短移植开发时间。此外,7 系列 FPGA 逻辑阵列和 DSP 架构均基于 Virtex-6 架构之上,因此开发人员现在就能启动设计工作,并轻松将其升级到 7 系列产品上,以充分利用 28nm 工艺技术的优势。

如果系统使用波束形成器 ASIC, 那么每次都需要设计新的 ASIC (将近耗费 100 万美元的成本),或是需要为小型设计使用超大型器件,这就会导致供应商不得不为不能被充分利用的芯片硬件支付额外成本。赛灵思的通用架构不仅能够在设计的重新调整过程中最大限度地降低 NRE 成本,而且还使设计人员能为全新的系统采用效率最高的FPGA 器件。

就其他 FPGA 而言,工程师往往需要耗费数月的时间进行调整并重复验证所购买的专有 IP 模块才能适应架构转换的需要,而后还要再花几个月的时间确认代码修改后新优化的设计方案。如果采用 7 系列 FPGA 的统一架构,我们就能大幅缩短开发时间,确保用户快速在整个产品系列中实现设计模块的移植。此外,IP 核的可用性也能显著获得提升,因为赛灵思和 IP 核合作伙伴仅需一次性优化 IP 核即可,随后就能根据不同的器件要求加以调整,从而尽可能减少修改幅度,而且每个系列的重复验证也会很方便。统一架构的另一优势在于其能在较短的时间内为新的超生系统获得医疗设备认证,因为大部分 HDL 代码都能在不同产品系列上实现重复利用,在某些情况下甚至包括网表的重复利用。

总而言之,赛灵思的通用架构能大幅提高超声系统供应商的规模经济效益,帮助他们 提供多种不同的系统功能和复杂性选择,同时还能缩短开发时间和产品的批准认证时 间,使供应商能够更方便地根据不同应用需求使用性价比最高的器件。

#### 赛灵思 IP 核

赛灵思 IP 核是赛灵思设计方案的关键构建块。种类丰富的基础 IP核可满足 FPGA 设计人员的一般性需求,而稳健可靠的特定领域和特定市场 IP核则能满足 DSP、嵌入式和连接设计的特定需求。超声系统所需的众多关键 DSP 功能和连接接口都可作为赛灵思或合作伙伴的 IP 核提供。使用赛灵思 IP 核不仅能够最大限度地缩短开发时间,并且还能帮助用户集中精力实现产品差异化设计,而非标准功能开发——这是使用赛灵思产品的一项独到的优势。

如欲了解赛灵思 IP 核的更多详情, 敬请访问: http://www.xilinx.com/ipcenter/。

### 总结

Spartan-6、Virtex-6 和 7 系列 FPGA 均可提供专用 ASIC 和 DSP 的高性能,同时还具备 极低 NRE 成本、大幅缩短产品上市时间、便于设计移植、高 I/O 数量和 PCB 布局简 化等优势。此外,配合业界领先的功耗优化工具,赛灵思的 40nm 和即将推出的 28nm FPGA 定制低功耗工艺技术还能大幅降低功耗,显著优于业界同类型的竞争解决方案。上述所有优势都能帮助便携式超声系统开发人员快速部署系统,在预算和功耗要求限度内推出最新技术,从而改进患者的护理工作。

### 修订历史

下表列出了本文的修订历史:

| 日期          | 版本  | 修订描述    |

|-------------|-----|---------|

| 2010年10月27日 | 1.0 | 赛灵思初始版本 |

#### Notice of Disclaimer

The information disclosed to you hereunder (the "Information") is provided "AS-IS" with no warranty of any kind, express or implied. Xilinx does not assume any liability arising from your use of the Information. You are responsible for obtaining any rights you may require for your use of this Information. Xilinx reserves the right to make changes, at any time, to the Information without notice and at its sole discretion. Xilinx assumes no obligation to correct any errors contained in the Information or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE INFORMATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.