# Introduction to FPGA Design with Vivado High-Level Synthesis

UG998 (v1.0) July 2, 2013

#### **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

© Copyright 2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, ARM, and Cortex are trademarks of ARM in the EU and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                |

|------------|---------|-------------------------|

| 07/02/2013 | 1.0     | Initial Xilinx release. |

# **Table of Contents**

| Revision History                                | 2   |

|-------------------------------------------------|-----|

| Chapter 1: Introduction                         |     |

| Overview                                        | . 5 |

| Programming Model                               | . 6 |

| Guide Organization                              | . 8 |

| Chapter 2: What is an FPGA?                     |     |

| Overview                                        | 11  |

| FPGA Architecture                               | 11  |

| FPGA Parallelism Versus Processor Architectures | 17  |

| Chapter 3: Basic Concepts of Hardware Design    |     |

| Overview                                        | 23  |

| Clock Frequency                                 | 23  |

| Latency and Pipelining                          | 27  |

| Throughput                                      | 28  |

| Memory Architecture and Layout                  | 29  |

| Chapter 4: Vivado High-Level Synthesis          |     |

| Overview                                        | 32  |

| Operations                                      | 32  |

| Conditional Statements                          | 35  |

| Loops                                           | 36  |

| Functions                                       | 38  |

| Dynamic Memory Allocation                       | 38  |

| Pointers                                        | 40  |

| Chapter 5: Computation-Centric Algorithms       |     |

| Overview                                        | 42  |

| Data Rate Optimization                          | 44  |

| Chapter 6: Control-Centric Algorithms                     |    |

|-----------------------------------------------------------|----|

| Overview                                                  | 50 |

| Expressing Control in C/C++                               | 50 |

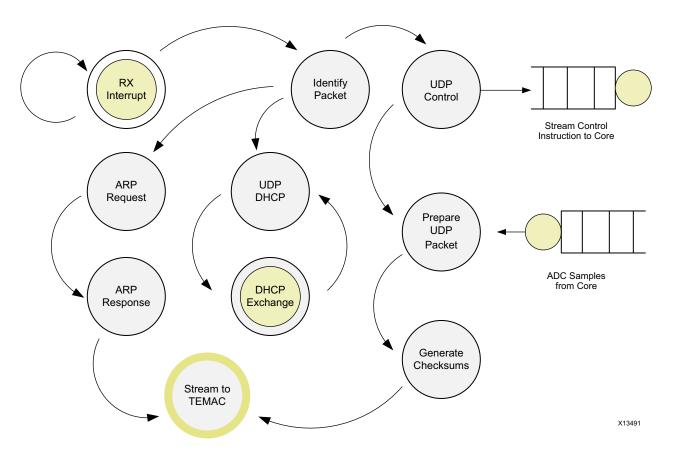

| UDP Packet Processing                                     | 55 |

| Chapter 7: Software Verification and Vivado HLS           |    |

| Overview                                                  | 60 |

| Software Test Bench                                       | 60 |

| Code Coverage                                             | 62 |

| Uninitialized Variables                                   | 63 |

| Out-of-Bounds Memory Access                               | 64 |

| Co-Simulation                                             | 65 |

| When C/C++ Verification Is Not Possible                   | 67 |

| Chapter 8: Integration of Multiple Programs               |    |

| Overview                                                  | 68 |

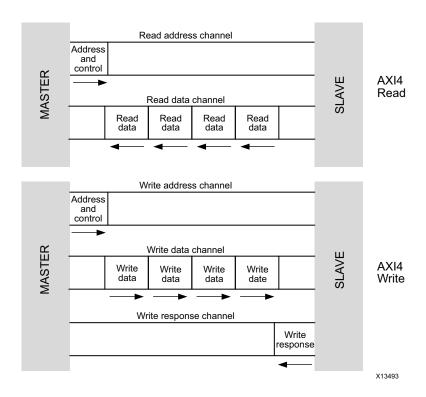

| AXI                                                       | 68 |

| Design Example: Application Running on a Zynq-7000 AP SoC | 72 |

| Chapter 9: Verification of a Complete Application         |    |

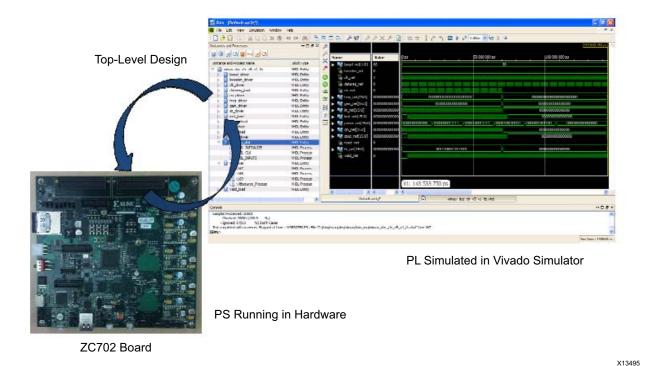

| Overview                                                  | 83 |

| Standalone Compute Systems                                |    |

| Processor-Based Systems                                   |    |

| Amondiu A. Additional Descurses                           |    |

| Appendix A: Additional Resources                          |    |

| Xilinx Resources                                          |    |

| Solution Centers                                          | 89 |

| Defenses                                                  | 00 |

# Introduction

## **Overview**

Software is the basis of all applications. Whether for entertainment, gaming, communications, or medicine, many of the products people use today began as a software model or prototype. Based on the performance and programmability constraints of the system, the software engineer is tasked with determining the best implementation platform to get a project to market. To accomplish this task, the software engineer is aided by both programming techniques and a variety of hardware processing platforms.

On the programming side, previous decades yielded advances in object-oriented programming for code reuse and parallel computing paradigms for boosting algorithm performance. The advancements in programming languages, frameworks, and tools allowed the software engineer to quickly prototype and test different approaches to solve a particular problem. This need to quickly prototype a solution leads to two interesting questions. The first question of how to analyze and quantify one algorithm against another is extensively discussed in other works and is not the focus of this guide. The second question of where to execute the algorithm is addressed in this guide in relation to field programmable gate arrays (FPGAs).

Regarding where to run an algorithm, there is an increasing focus on parallelization and concurrency. Although the interest in the parallel and concurrent execution of software programs is not new, the renewed and increased interest is aided by certain trends in processor and application-specific integrated circuit (ASIC) design. In the past, the software engineer faced two choices for getting more performance out of a software algorithm: a custom-integrated circuit or an FPGA.

The first and most expensive option is to turn the algorithm over to a hardware engineer for a custom circuit implementation. The cost of this option is based on:

- Cost to fabricate the circuit

- Time to translate the algorithm into hardware

Despite advancements in fabrication process node technology that have yielded significant improvements in power consumption, computational throughput, and logic density, the cost to fabricate a custom-integrated circuit or ASIC for an application is still high. At each processing node, the cost of fabrication continues to increase to the point where this

approach is only economically viable for applications that ship in the range of millions of units.

The second option is to use an FPGA, which addresses the cost issues inherent in ASIC fabrication. FPGAs allow the designer to create a custom circuit implementation of an algorithm using an off-the-shelf component composed of basic programmable logic elements. This platform offers the power consumption savings and performance benefits of smaller fabrication nodes without incurring the cost and complexity of an ASIC development effort. Similar to an ASIC, an algorithm implemented in an FPGA benefits from the inherent parallel nature of a custom circuit.

## **Programming Model**

The programming model of a hardware platform is one of the driving factors behind its adoption. Software algorithms are typically captured in C/C++ or some other high-level language, which abstracts the details of the computing platform. These languages allow for quick iteration, incremental improvements, and code portability, which are critical to the software engineer. For the past few decades, the fast execution of algorithms captured in these languages have fueled the development of processors and software compilers.

Initially, improving the runtime of software was based on two central concepts: increasing processor clock frequency and using specialized processors. For many years, it was common practice to wait a year for the next generation processor as a way to speed up execution. At every new higher clock frequency, the software program ran faster. Although this was acceptable in some cases, for a large set of applications, incremental speedup through processor clock frequency is not enough to deliver a viable product to market.

For this type of application, the specialized processor was created. Although there are many kinds of specialized processors, such as the digital signal processor (DSP) and graphics processing unit (GPU), all of these processors are capable of executing an algorithm written in a high-level language, such as C, and have function-specific accelerators to improve the execution of their target software applications.

With the recent paradigm shift in the design of standard and specialized processors, both types of processors stopped relying on clock frequency increases for program speedup and added more processing cores per chip. Multicore processors put program parallelization at the forefront of techniques used to boost software performance. The software engineer must now structure algorithms in a way that leads to efficient parallelization for performance. The techniques required in algorithm design use the same base elements of FPGA design. The main difference between an FPGA and a processor is the programming model.

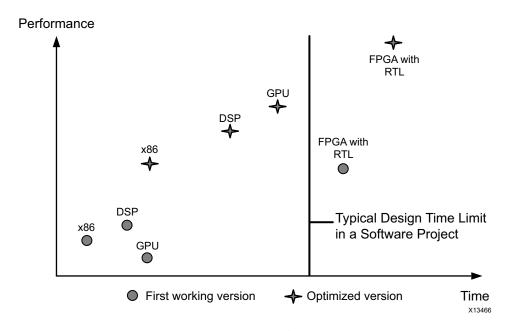

Historically, the programming model of an FPGA was centered on register-transfer level (RTL) descriptions instead of C/C++. Although this model of design capture is completely compatible with ASIC design, it is analogous to assembly language programming in software engineering. Figure 1-1 shows a traditional FPGA design flow with RTL as the design capture method, which illustrates how the programming model difference affects implementation time and achievable performance for different computation platforms.

Figure 1-1: Design Time vs. Application Performance with RTL Design Entry

As shown in Figure 1-1, arriving at an initial working version of a software program occurs relatively quickly in the project design cycle for both standard and specialized processors. After the initial working version, additional development effort must be allotted to achieve maximum performance on any implementation platform.

This figure also shows the time it takes to develop the same software application for an FPGA platform. Both the initial and optimized versions of an application provide significant performance when compared against the same stages for both standard and specialized processors. RTL coding and an FPGA optimized application result in the highest performance implementation.

However, the development time required to arrive at this implementation is beyond the scope of a typical software development effort. Therefore, FPGAs were traditionally used only for those applications requiring a performance profile that could not be achieved by any other means, such as designs with multiple processors.

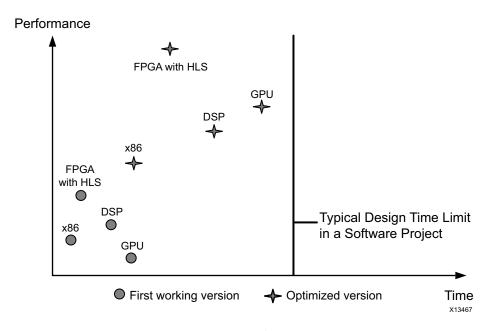

Recent technological advances by Xilinx® remove the difference in programming models between a processor and an FPGA. Just as there are compilers from C and other high-level languages to different processor architectures, the Xilinx Vivado® High-Level Synthesis (HLS) compiler provides the same functionality for C/C++ programs targeted to Xilinx FPGAs. Figure 1-2 compares the result of the HLS compiler against other processor solutions available to a software engineer.

Figure 1-2: Design Time vs. Application Performance with Vivado HLS Compiler

# **Guide Organization**

There is a significant difference between the performance of an FPGA and other processors for the same C/C++ application. The following chapters in this guide describe the reasons behind this dramatic performance difference and introduce how the Vivado HLS compiler works.

#### Chapter 2: What is an FPGA?

Chapter 2, What is an FPGA? introduces the computational elements available in an FPGA and how they compare to a processor. It covers topics such as FPGA memory hierarchy, logic elements, and how these elements interrelate.

#### **Chapter 3: Basic Concepts of Hardware Design**

The difference between the hardware of a processor and an FPGA affects how a compiler for each target works. Chapter 3, Basic Concepts of Hardware Design covers fundamental

hardware concepts that apply to both FPGA and processor-based designs. Understanding these concepts assists the designer in guiding the Vivado HLS compiler to create the best processing architecture.

#### **Chapter 4: Vivado High-Level Synthesis**

Chapter 4, Vivado High-Level Synthesis introduces the Xilinx Vivado HLS compiler. Using concepts from the preceding two chapters, this section describes how a C/C++ program is compiled for an FPGA. This chapter focuses on how the compiler extracts parallelism, organizes memory, and connects multiple programs within an FPGA.

#### **Chapter 5: Computation-Centric Algorithms**

Although there is extensive literature on algorithm analysis, the nuances of computation-versus control-centric algorithms are largely dependent on the implementation platform. Chapter 5, Computation-Centric Algorithms defines computation-centric algorithms for an FPGA and provides examples and best practice recommendations.

#### **Chapter 6: Control-Centric Algorithms**

Control-centric algorithms can be implemented on both processors and FPGAs. The implementation choice depends on the reaction time required of the algorithm. Chapter 6, Control-Centric Algorithms provides an overview of control-centric algorithm implementation options and provides a networking example for user datagram protocol (UDP) packet processing.

## **Chapter 7: Software Verification and Vivado HLS**

As with all compilers, the quality and correctness of the HLS compiler output depends on the input software. Chapter 7, Software Verification and Vivado HLS reviews recommended software quality techniques that apply to the Vivado HLS compiler. It presents examples of typical coding errors and their effect on HLS compilation as well as possible solutions to each problem. It also includes a section on what to do when program behavior cannot be fully verified at the C level.

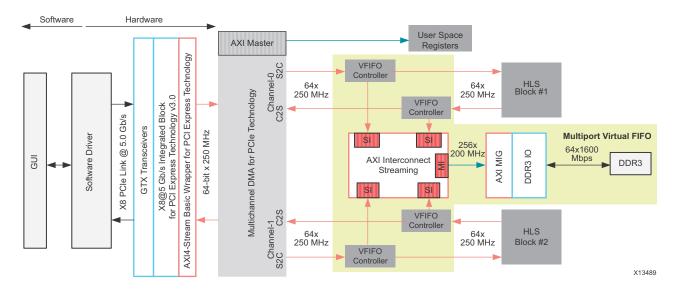

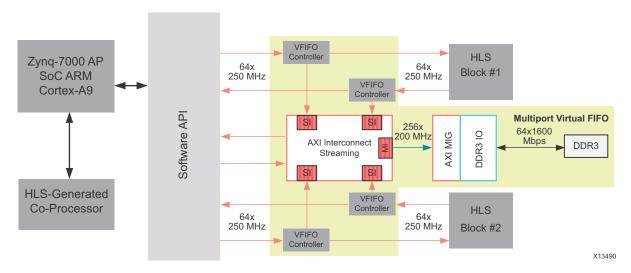

## **Chapter 8: Integration of Multiple Programs**

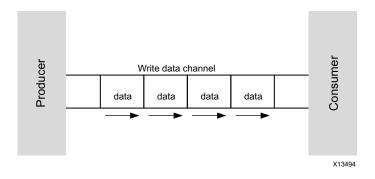

Just as most processors run multiple programs to execute an application, an FPGA can also build multiple programs or modules to execute a specific application. Chapter 8, Integration of Multiple Programs describes how to connect multiple modules in an FPGA and how to control these modules with a processor. It highlights the Xilinx Zynq®-7000 All Programmable (AP) System on a Chip (SoC), which combines FPGA fabric with ARM® Cortex™-A9 processors. Using both a consumer and producer example, this chapter also demonstrates complete system development, integration, and design trade-offs.

## **Chapter 9: Verification of a Complete Application**

With an FPGA, a complete application creates a hardware system. This system can have one or more modules in the FPGA fabric as well as code executing on a processor. Chapter 9, Verification of a Complete Application provides recommendations and best practices to ensure correct execution of the target application.

# What is an FPGA?

## **Overview**

An FPGA is a type of integrated circuit (IC) that can be programmed for different algorithms after fabrication. Modern FPGA devices consist of up to two million logic cells that can be configured to implement a variety of software algorithms. Although the traditional FPGA design flow is more similar to a regular IC than a processor, an FPGA provides significant cost advantages in comparison to an IC development effort and offers the same level of performance in most cases. Another advantage of the FPGA when compared to the IC is its ability to be dynamically reconfigured. This process, which is the same as loading a program in a processor, can affect part or all of the resources available in the FPGA fabric.

When using the Vivado® HLS compiler, it is important to have a basic understanding of the available resources in the FPGA fabric and how they interact to execute a target application. This chapter presents fundamental information about FPGAs, which is required to guide HLS to the best computational architecture for any algorithm.

## **FPGA Architecture**

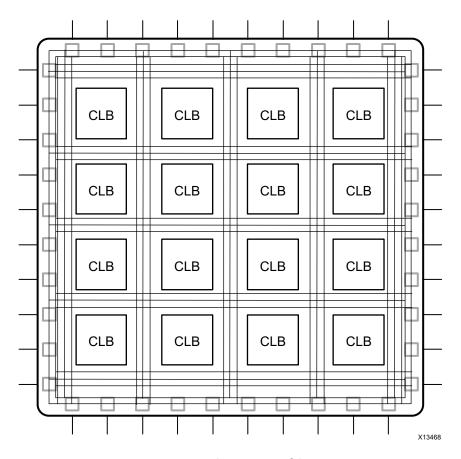

The basic structure of an FPGA is composed of the following elements:

- **Look-up table (LUT)**: This element performs logic operations.

- **Flip-Flop (FF)**: This register element stores the result of the LUT.

- Wires: These elements connect elements to one another.

- Input/Output (I/O) pads: These physically available ports get data in and out of the FPGA.

The combination of these elements results in the basic FPGA architecture shown in Figure 2-1. Although this structure is sufficient for the implementation of any algorithm, the efficiency of the resulting implementation is limited in terms of computational throughput, required resources, and achievable clock frequency.

Figure 2-1: Basic FPGA Architecture

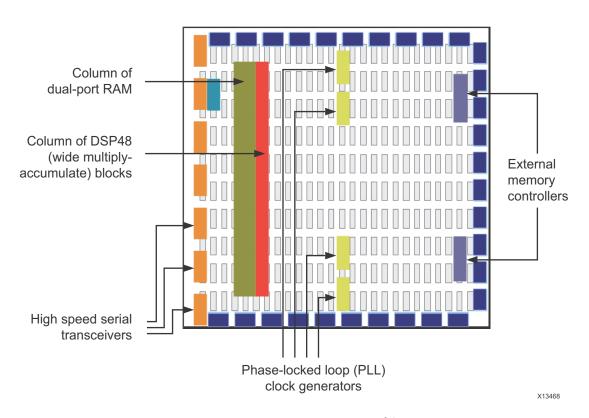

Contemporary FPGA architectures incorporate the basic elements along with additional computational and data storage blocks that increase the computational density and efficiency of the device. These additional elements, which are discussed in the following sections, are:

- Embedded memories for distributed data storage

- Phase-locked loops (PLLs) for driving the FPGA fabric at different clock rates

- High-speed serial transceivers

- Off-chip memory controllers

- Multiply-accumulate blocks

The combination of these elements provides the FPGA with the flexibility to implement any software algorithm running on a processor and results in the contemporary FPGA architecture shown in Figure 2-2.

Figure 2-2: Contemporary FPGA Architecture

#### LUT

The LUT is the basic building block of an FPGA and is capable of implementing any logic function of *N* Boolean variables. Essentially, this element is a truth table in which different combinations of the inputs implement different functions to yield output values. The limit on the size of the truth table is *N*, where *N* represents the number of inputs to the LUT. For the general *N*-input LUT, the number of memory locations accessed by the table is:

which allows the table to implement the following number of functions:

$$2^{N^{N}}$$

Equation 2-2

**Note:** A typical value for N in Xilinx FPGA devices is 6.

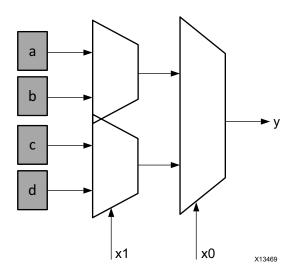

The hardware implementation of a LUT can be thought of as a collection of memory cells connected to a set of multiplexers. The inputs to the LUT act as selector bits on the multiplexer to select the result at a given point in time. It is important to keep this representation in mind, because a LUT can be used as both a function compute engine and a data storage element. Figure 2-3 shows this functional representation of the LUT.

Figure 2-3: Functional Representation of a LUT as Collection of Memory Cells

#### Flip-Flop

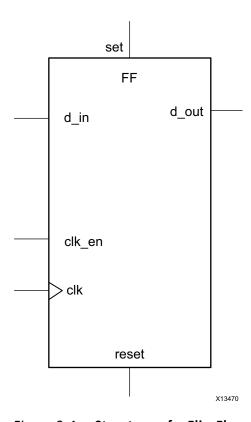

The flip-flop is the basic storage unit within the FPGA fabric. This element is always paired with a LUT to assist in logic pipelining and data storage. The basic structure of a flip-flop includes a data input, clock input, clock enable, reset, and data output. During normal operation, any value at the data input port is latched and passed to the output on every pulse of the clock. The purpose of the clock enable pin is to allow the flip-flop to hold a specific value for more than one clock pulse. New data inputs are only latched and passed to the data output port when both clock and clock enable are equal to one. Figure 2-4 shows the structure of a flip-flop.

Figure 2-4: Structure of a Flip-Flop

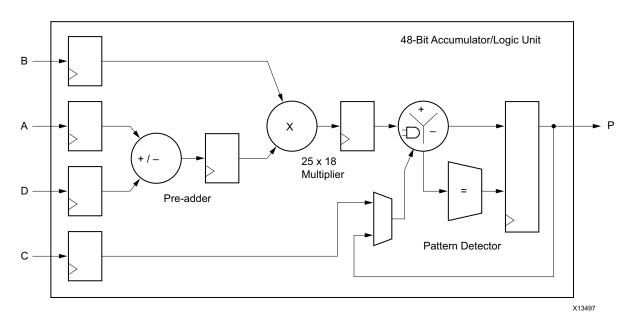

#### **DSP48 Block**

The most complex computational block available in a Xilinx FPGA is the DSP48 block, which is shown in Figure 2-5. The DSP48 block is an arithmetic logic unit (ALU) embedded into the fabric of the FPGA, which is composed of a chain of three different blocks. The computational chain in the DSP48 is composed of an add/subtract unit connected to a multiplier connected to a final add/subtract/accumulate engine. This chain allows a single DSP48 unit to implement functions of the form:

$$p = a \times (b+d) + c$$

Equation 2-3

or

$$p += a \times (b + d)$$

Equation 2-4

Figure 2-5: Structure of a DSP48 Block

#### **BRAM and Other Memories**

The FPGA fabric includes embedded memory elements that can be used as random-access memory (RAM), read-only memory (ROM), or shift registers. These elements are block RAMs (BRAMs), LUTs, and shift registers.

The BRAM is a dual-port RAM module instantiated into the FPGA fabric to provide on-chip storage for a relatively large set of data. The two types of BRAM memories available in a device can hold either 18 k or 36 k bits. The number of these memories available is device specific. The dual-port nature of these memories allows for parallel, same-clock-cycle access to different locations.

In terms of how arrays are represented in C/C++ code, BRAMs can implement either a RAM or a ROM. The only difference is when the data is written to the storage element. In a RAM

configuration, the data can be read and written at any time during the runtime of the circuit. In contrast, in a ROM configuration, data can only be read during the runtime of the circuit. The data of the ROM is written as part of the FPGA configuration and cannot be modified in any way.

As previously discussed, the LUT is a small memory in which the contents of a truth table are written during device configuration. Due to the flexibility of the LUT structure in Xilinx FPGAs, these blocks can be used as 64-bit memories and are commonly referred to as distributed memories. This is the fastest kind of memory available on the FPGA device, because it can be instantiated in any part of the fabric that improves the performance of the implemented circuit.

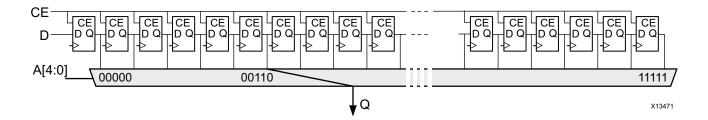

The shift register is a chain of registers connected to each other. The purpose of this structure is to provide data reuse along a computational path, such as with a filter. For example, a basic filter is composed of a chain of multipliers that multiply a data sample against a set of coefficients. By using a shift register to store the input data, a built-in data transport structure moves the data sample to the next multiplier in the chain on every clock cycle. Figure 2-6 shows an example shift register.

Figure 2-6: Structure of an Addressable Shift Register

## **FPGA Parallelism Versus Processor Architectures**

When compared with processor architectures, the structures that comprise the FPGA fabric enable a high degree of parallelism in application execution. The custom processing architecture generated by the HLS compiler for a software program presents a different execution paradigm, which must be taken into account when deciding to port an application from a processor to an FPGA. To examine the benefits of the FPGA execution paradigm, this section provides a brief review of processor program execution.

#### **Program Execution on a Processor**

A processor, regardless of its type, executes a program as a sequence of instructions that translate into useful computations for the software application. This sequence of instructions is generated by processor compiler tools, such as the GNU Compiler Collection (GCC), which transform an algorithm expressed in C/C++ into assembly language

constructs that are native to the processor. The job of a processor compiler is to take a C function of the form:

$$z = a + b$$

; Equation 2-5

and transform it into assembly code as follows:

Figure 2-7: Computation Expressed Assembly Code

The assembly code in Figure 2-7 defines the addition operation to compute the value of z in terms of the internal registers of a processor. The code states that the input values for the computation are stored in registers R1 and R2, and the result of the computation is stored in register R3. This code is simple, and it does not express all the instructions needed to compute the value of z. This code only handles the computation after the data has arrived at the processor. Therefore, the compiler must create additional assembly language instructions to load the registers of the processor with data from a central memory and to write back the result to memory. The complete assembly program to compute the value of z is as follows:

```

LD a, $R1

LD b, $R2

ADD $R1,$R2,$R3

ST $R3, c

```

Figure 2-8: Complete Assembly Program to Compute Z

The code in Figure 2-8 shows that even a simple operation, such as the addition of two values, results in multiple assembly instructions. The computational latency of each instruction is not equal across instruction types. For example, depending on the location of a and b, the LD operations take a different number of clock cycles to complete. If the values are in the processor cache, these load operations complete within a few tens of clock cycles. If the values are in the main, double data rate (DDR) memory, the operations take between hundreds and thousands of clock cycles to complete. If the values are in a hard drive, the load operations take even longer to complete. This is why software engineers with cache hit traces spend so much time restructuring their algorithms to increase the spatial locality of data in memory to increase the cache hit rate and decrease the processor time spent per instruction.

**IMPORTANT:** The level of effort required by the software engineer in restructuring algorithms to better fit the available processor cache is not required when the same operation is implemented in an FPGA.

#### **Program Execution on an FPGA**

The FPGA is an inherently parallel processing fabric capable of implementing any logical and arithmetic function that can run on a processor. The main difference is that the HLS compiler, which is used to transform software descriptions into RTL, is not hindered by the restrictions of a cache and a unified memory space.

The computation of z is compiled by HLS into several LUTs required to achieve the size of the output operand. For example, assume that in the original software program the variable a, b, and z are defined with the short data type. This type, which defines a 16-bit data container, gets implemented as 16 LUTs by HLS.

**Note:** As a general rule, 1 LUT is equivalent to 1 bit of computation.

The LUTs used for the computation of z are exclusive to this operation only. Unlike a processor, where all computations share the same ALU, an FPGA implementation instantiates independent sets of LUTs for each computation in the software algorithm.

In addition to assigning unique LUT resources per computation, the FPGA differs from a processor in both memory architecture and the cost of memory accesses. In an FPGA implementation, the HLS compiler arranges memories into multiple storage banks as close as possible to the point of use in the operation. This results in an instantaneous memory bandwidth, which far exceeds the capabilities of a processor. For example, the Xilinx Kintex®-7 410T device has a total of 1,590 18 k-bit BRAMs available. In terms of memory bandwidth, the memory layout of this device provides the software engineer with the capacity of 0.5M-bits per second at the register level and 23T-bits per second at the BRAM level.

With regard to computational throughput and memory bandwidth, the HLS compiler exercises the capabilities of the FPGA fabric through the processes of scheduling, pipelining, and dataflow. Although transparent to the user, these processes are integral stages of the software compilation process that extract the best possible circuit-level implementation of the software application.

#### Scheduling

Scheduling is the process of identifying the data and control dependencies between different operations to determine when each will execute. In traditional FPGA design, this is a manual process also referred to as parallelizing the software algorithm for a hardware implementation.

HLS analyzes dependencies between adjacent operations as well as across time. This allows the compiler to group operations to execute in the same clock cycle and to set up the hardware to allow the overlap of function calls. The overlap of function call executions removes the processor restriction that requires the current function call to fully complete before the next function call to the same set of operations can begin. This process is called *pipelining* and is covered in detail in the following section and remaining chapters.

#### **Pipelining**

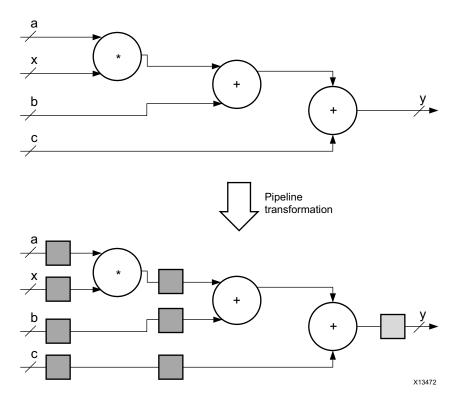

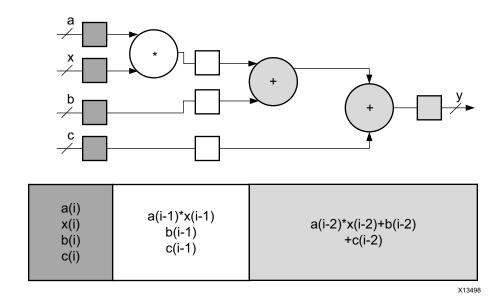

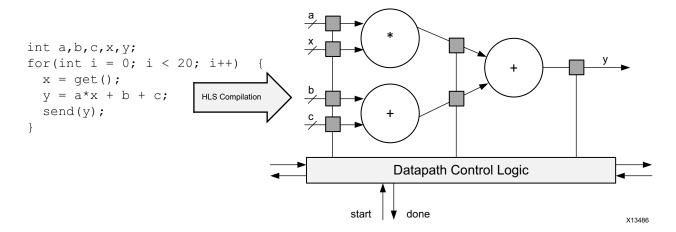

Pipelining is a digital design technique that allows the designer to avoid data dependencies and increase the level of parallelism in an algorithm hardware implementation. The data dependence in the original software implementation is preserved for functional equivalence, but the required circuit is divided into a chain of independent stages. All stages in the chain run in parallel on the same clock cycle. The only difference is the source of data for each stage. Each stage in the computation receives its data values from the result computed by the preceding stage during the previous clock cycle. For example, to compute the following function the HLS compiler instantiates one multiplier and two adder blocks:

$$y = (a \times x) + b + c$$

Equation 2-6

Figure 2-9 shows this compute structure and the effects of pipelining. It shows two implementations of the example function. The top implementation is the datapath required to compute the result *y* without pipelining. This implementation behaves similarly to the corresponding C/C++ function in that all input values must be known at the start of the computation, and only one result *y* can be computed at a time. The bottom implementation shows the pipelined version of the same circuit.

Figure 2-9: FPGA Implementation of a Compute Function

The boxes in the datapath in Figure 2-9 represent registers that are implemented by flip-flop blocks in the FPGA fabric. Each box can be counted as a single clock cycle. Therefore, in the pipelined version, the computation of each result *y* takes three clock

cycles. By adding the register, each block is isolated into separate compute sections in time. This means that the section with the multiplier and the section with the two adders can run in parallel and reduce the overall computational latency of the function. By running both sections of the datapath in parallel, the block is essentially computing the values y and y' in parallel, where y' is the result of the next execution of Equation 2-6. The initial computation of y, which is also referred to as the *pipeline fill time*, takes three clock cycles. After this initial computation, a new value of y is available at the output on every clock cycle, because the computation pipeline contains overlapped data sets for the current and subsequent y computations.

Figure 2-10 shows a pipelined architecture in which raw data (dark gray), semi-computed data (white), and final data (light gray) exist simultaneously, and each stage result is captured in its own set of registers. Thus, although the latency for such computation is in multiple cycles, with every cycle a new result can be produced.

Figure 2-10: Pipelined Architecture

#### **Dataflow**

Dataflow is another digital design technique, which is similar in concept to pipelining. The goal of dataflow is to express parallelism at a coarse-grain level. In terms of software execution, this transformation applies to parallel execution of functions within a single program.

HLS extracts this level of parallelism by evaluating the interactions between different functions of a program based on their inputs and outputs. The simplest case of parallelism is when functions work on different data sets and do not communicate with each other. In this case, HLS allocates FPGA logic resources for each function and then runs the blocks in independently. The more complex case, which is typical in software programs, is when one

function provides results for another function. This case is referred to as the consumer-producer scenario.

HLS supports two use models for the consumer-producer scenario. In the first use model, the producer creates a complete data set before the consumer can start its operation. Parallelism is achieved by instantiating a pair of BRAM memories arranged as memory banks ping and pong. Each function can access only one memory bank, ping or pong, for the duration of a function call. When a new function call begins, the HLS-generated circuit switches the memory connections for both the producer and the consumer. This approach guarantees functional correctness but limits the level of achievable parallelism to across function calls.

In the second use model, the consumer can start working with partial results from the producer, and the achievable level of parallelism is extended to include execution within a function call. The HLS-generated modules for both functions are connected through the use of a first in, first out (FIFO) memory circuit. This memory circuit, which acts as a queue in software programming, provides data-level synchronization between the modules. At any point during a function call, both hardware modules are executing their programming. The only exception is that the consumer module waits for some data to be available from the producer before beginning computation. In HLS terminology, the wait time of the consumer module is referred to as the *interval* or *initiation interval* (II).

# Basic Concepts of Hardware Design

## **Overview**

One of the key differences between a processor and an FPGA is whether the processing architecture is fixed. This difference directly affects how a compiler for each target works. With a processor, the computation architecture is fixed, and the job of the compiler is to determine how to best fit the software application in the available processing structures. Performance is a function of how well the application maps to the capabilities of the processor and the number of processor instructions needed for correct execution.

In contrast, an FPGA is similar to a blank slate with a box of building blocks. The job of the Vivado® HLS compiler is to create a processing architecture from the box of building blocks that best fits the software program. The process of guiding the HLS compiler to create the best processing architecture requires fundamental knowledge about hardware design concepts.

This chapter covers general design concepts that apply to both FPGA and processor-based designs and explains how these concepts are related. This chapter does not cover detailed aspects of FPGA design. As with processor compilers, the HLS compiler handles the low-level details of the algorithm implementation into the FPGA logic fabric.

# **Clock Frequency**

The processor clock frequency is one of the first items to consider when determining the execution platform of a specific algorithm. A commonly used guideline is that a high clock frequency translates into a higher performance execution rate of an algorithm. Although this might be a good first order rule for choosing between processors, it is actually misleading and can lead the designer to make the wrong choice when selecting between a processor and an FPGA.

The reason this general guideline is misleading is related to the nominal difference in clock frequency between a processor and an FPGA. For example, when comparing the clock frequencies of processors and FPGAs, it is not uncommon to face the comparison shown in Table 3-1.

Table 3-1: Maximum Clock Frequency Examples

| Processor | FPGA    |

|-----------|---------|

| 2 GHz     | 500 MHz |

A simple analysis of the values in Table 3-1 can mislead a designer to assume the processor has four times the performance of the FPGA. This simple analysis incorrectly assumes that the only difference between the platforms is clock frequency. However, the platforms have additional differences.

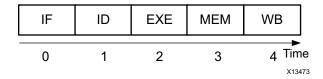

The first major difference between a processor and an FPGA is how a software program is executed. A processor is able to execute any program on a common hardware platform. This common platform comprises the core of the processor and defines a fixed architecture onto which all software must be fitted. The compiler, which has a built-in understanding of the processor architecture, compiles the user software into a set of instructions. The resulting set of instructions is always executed in the same fundamental order, as shown in Figure 3-1.

Figure 3-1: Processor Instruction Execution Stages

Regardless of the type of processor, standard versus specialized, the execution of an instruction is always the same. Each instruction of the user application must go through the following stages:

- 1. Instruction fetch (IF)

- 2. Instruction decode (ID)

- 3. Execute (EXE)

- 4. Memory operations (MEM)

- 5. Write back (WB)

The purpose of each stage is summarized in Table 3-2.

**Table 3-2:** Instruction Processing Stages

| Stage | Description                                                                                                                                                                                                                                                                                             |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IF    | Get the instruction from program memory.                                                                                                                                                                                                                                                                |  |

| ID    | Decode the instruction to determine the operation and the operators.                                                                                                                                                                                                                                    |  |

| EXE   | Execute the instruction on the available hardware. In a standard processor, this means the arithmetic logic unit (ALU) or floating point unit (FPU). A specialized processor adds on fixed function accelerators to the capabilities of the standard processor at this stage of instruction processing. |  |

| MEM   | Fetch data for the next instruction using memory operations.                                                                                                                                                                                                                                            |  |

| WB    | Write the results of the instruction either to local registers or global memory.                                                                                                                                                                                                                        |  |

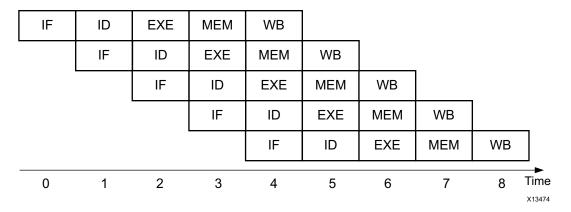

Most modern processors include multiple copies of the instruction execution path and are capable of running instructions with some degree of overlap. Because instructions in a processor usually depend on each other, the overlap between copies of the instruction execution hardware is not perfect. In the best of cases, only the overhead stages introduced by using a processor can be overlapped. The EXE stages, which are responsible for application computation, execute sequentially. The reasons for this sequential execution are related to limited resources in the EXE stage and dependence between instructions.

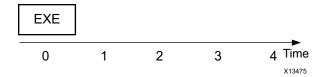

Figure 3-2 shows a processor with multiple instructions executing in a semi-parallel order. This is the best case for a processor in which all instructions are executing as quickly as possible. Even in this best case, the processor is limited to only one EXE stage per clock cycle. This means that the user application moves forward by one operation per clock cycle. Even if the compiler determined that all five EXE stages could execute in parallel, the structure of the process would prevent it.

Figure 3-2: Processor with Multiple Instruction Execution Units

An FPGA does not execute all software on a common computation platform. It executes a single program at a time on a custom circuit for that program. Therefore, changing the user application changes the circuit in the FPGA. Unlike Figure 3-1, the EXE stage appears as shown in Figure 3-3 when processing in an FPGA. The presence of the MEM stage is application dependent.

Figure 3-3: FPGA Instruction Execution Stages

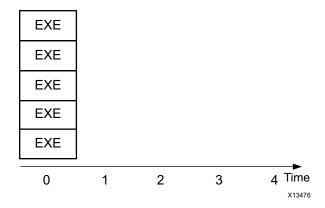

Given this flexibility, the HLS compiler does not need to account for overhead stages in the platform and can find ways of maximizing instruction parallelism. Working with the same assumptions as in Figure 3-2, the execution profile of the same software in an FPGA is shown in Figure 3-4.

Figure 3-4: FPGA with Multiple Instruction Execution Units

Based on the comparison of Figure 3-2 and Figure 3-4, the FPGA has a nominal performance advantage of 9x compared to the processor. Actual numbers are always application specific, but FPGAs generally demonstrate at least 10x the performance of a processor for computationally intensive applications.

Another issue hidden by only focusing on the clock frequency is the power consumption of a software program. The approximation to power consumption is given by:

$$P = \frac{1}{2}cFV^2$$

Equation 3-1

As shown in Equation 3-1, the relationship between power consumption and clock frequency is supported by empirical data, which shows higher power usage in a processor than an FPGA for the same computational workload. By creating a custom circuit per software program, an FPGA is able to run at a lower clock frequency with maximum parallelism between operations and without the instruction interpretation overhead found in a processor.

**RECOMMENDED:** When selecting between a processor and an FPGA, it is recommended that application requirements and computational workload are analyzed based on throughput and latency instead of a maximum clock frequency.

# **Latency and Pipelining**

Latency is the number of clock cycles it takes to complete an instruction or set of instructions to generate an application result value. Using the basic processor architecture shown in Figure 3-1, the latency of an instruction is five clock cycles. If the application has a total of five instructions, the overall latency for this simple model is 25 clock cycles. That is, the result of the application is not available until 25 clock cycles expire.

Application latency is a key performance metric in both FPGAs and processors. In both cases, the problem of latency is resolved through the use of pipelining. In a processor, pipelining means that the next instruction can be launched into execution before the current instruction is complete. This allows the overlap of overhead stages required in instruction set processing. The best case result of pipelining for a processor is shown in Figure 3-2. By overlapping the execution of instructions, the processor achieves a latency of nine clock cycles for the five instruction application.

In an FPGA, the overhead cycles associated with instruction processing are not present. The latency is measured by how many clock cycles it takes to run the EXE stage of the original processor instruction. For the case in Figure 3-3, the latency is one clock cycle. Parallelism also plays an important role in latency. For the full five instruction application, the FPGA latency is also one clock cycle, as shown in Figure 3-4. With the one clock cycle latency of the FPGA, it might not be clear why pipelining is advantageous. However, the reason for pipelining in an FPGA is the same as in a processor, that is, to improve application performance.

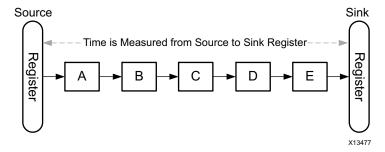

As previously explained, the FPGA is a blank slate with building blocks that must be connected to implement an application. The HLS compiler can connect the blocks directly or through registers. Figure 3-5 shows an implementation of the EXE stage in Figure 3-3 that is implemented using five building blocks.

Figure 3-5: FPGA Implementation without Pipelining

Operation timing in an FPGA is the length of time it takes a signal to travel from a source register to a sink register. Assuming each building block in Figure 3-5 requires 2 ns to execute, the current design requires 10 ns to implement the functionality. The latency is still one clock cycle, but the clock frequency is limited to 100 MHz. The 100 MHz frequency limit is derived from the definition of clock frequency in an FPGA. For the case of an FPGA circuit, the clock frequency is defined as the longest signal travel time between source and sink registers.

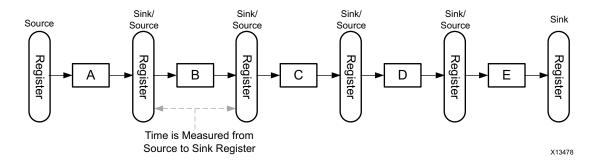

Pipelining in an FPGA is the process of inserting more registers to break up large computation blocks into smaller segments. This partitioning of the computation increases the latency in absolute number of clock cycles but increases performance by allowing the custom circuit to run at a higher clock frequency.

Figure 3-6 shows the implementation of the processing architecture in Figure 3-5 after complete pipelining. Complete pipelining means that a register is inserted between each building block in the FPGA circuit. The addition of registers reduces the timing requirement of the circuit from 10 ns to 2 ns, which results in a maximum clock frequency of 500 MHz. In addition, by separating the computation into separate register-bounded regions, each block is allowed to always be busy, which positively impacts the application throughput.

One issue with pipelining is the latency of the circuit. The original circuit of Figure 3-5 has a latency of one clock cycle at the expense of a low clock frequency. In contrast, the circuit of Figure 3-6 has a latency of five clock cycles at a higher clock frequency.

**IMPORTANT:** The latency caused by pipelining is one of the trade-offs to consider during FPGA design.

Figure 3-6: FPGA Implementation with Pipelining

# **Throughput**

Throughput is another metric used to determine overall performance of an implementation. It is the number of clock cycles it takes for the processing logic to accept the next input data sample. With this value, it is important to remember that the clock frequency of the circuit changes the meaning of the throughput number.

For example, both Figure 3-5 and Figure 3-6 show implementations that require one clock cycle between input data samples. The key difference is that the implementation in Figure 3-5 requires 10 ns between input samples, whereas the circuit in Figure 3-6 only requires 2 ns between input data samples. After the time base is known, it is clear that the second implementation has higher performance, because it can accept a higher input data rate.

**Note:** The definition of throughput described in this section can also be used when analyzing applications executing on a processor.

## **Memory Architecture and Layout**

The memory architecture of the selected implementation platform is one of the physical elements that can affect the performance of a software application. Memory architecture determines the upper bound on achievable performance. At some performance point, all applications on either a processor or an FPGA become memory bound regardless of the type and number of available computational resources. One strategy in FPGA design is understanding where the memory bound is and how it can be affected by data layout and memory organization.

In a processor-based system, the software engineer must fit the application on essentially the same memory architecture regardless of the specific type of processor. This commonality simplifies the process of application migration at the expense of performance. Common memory architecture familiar to software engineers consists of memories that are slow, medium, or fast based on the number of clock cycles it takes to get the data to the processor. These memory classifications are defined in Table 3-3.

| Table 3-3: | Memory Type | <b>Definitions</b> |

|------------|-------------|--------------------|

|------------|-------------|--------------------|

| Memory Type                                                                     | Definition                                |  |

|---------------------------------------------------------------------------------|-------------------------------------------|--|

| Slow                                                                            | Mass storage devices, such as hard drives |  |

| Medium                                                                          | DDR memories                              |  |

| Fast On-chip cache memories of different sizes depending on the specific proces |                                           |  |

The memory architecture shown in this table assumes that the user is presented with a single large memory space. Within this memory space, the user allocates and deallocates regions to store program data. The physical location of data and how it moves between the different levels in the hierarchy is handled by the computation platform and is transparent to the user. In this kind of system, the only way to boost performance is to reuse data in the cache as much as possible.

To achieve this goal, the software engineer must spend large amounts of time looking at cache traces, restructuring the software algorithm to increase data locality, and managing memory allocation to minimize the instantaneous memory footprint of the program. Although all of these techniques are portable across processors, the results are not. A software program must be tuned for each processor it runs on to maximize performance.

With experience in working with processor-based memory, the first difference a software engineer encounters when working with memory in an FPGA is the lack of fixed on-chip memory architecture. FPGA-based systems can be attached to slow and medium memories but exhibit the greatest degree of differentiation in terms of available fast memories. That is, instead of restructuring the software to best use an existing cache, the HLS compiler builds a fast memory architecture to best fit the data layout in the algorithm. The resulting FPGA implementation can have one or more internal banks of different sizes that can be accessed independently from one another.

The code examples in Figure 3-7 show best practice recommendations for addressing the memory requirements of a program.

#### **Processor Code**

#### FPGA Code

```

void foo(....)

{

int *A = (int *)malloc(10 * sizeof(int));

....

free(A);

}

```

```

void foo(.....)

{

int A[10];

....

}

```

Figure 3-7: Processor and FPGA Code Examples

The FPGA code might surprise a seasoned software engineer with its lack of dynamic memory allocation. The use of dynamic memory allocation has long been part of the best practice guidelines for processor-based systems due to the underlying fixed memory architecture.

In contrast to this approach, the HLS compiler builds a memory architecture that is tailored to the application. This tailored memory architecture is shaped both by the size of the memory blocks in the program as well as by how the data is used throughout program execution. Current state-of-the-art compilers for FPGAs, such as HLS, require that the memory requirements of an application are fully analyzable at compile time.

The benefit of static memory allocation is that HLS can implement the memory for array  $\mathbb{A}$  in different ways. Depending on the computation in the algorithm, the HLS compiler can implement the memory for  $\mathbb{A}$  as registers, shift registers, FIFOs, or BRAMs.

**Note:** Despite the restriction on dynamic memory allocation, pointers are fully supported by the HLS compiler. For details on pointer support, see Pointers in Chapter 4.

## Registers

A register implementation of a memory is the fastest possible memory structure. In this implementation style, each entry of A becomes an independent entity. Each independent entity is embedded into the computation where it is used without the need to address logic or additional delays.

#### **Shift Register**

In processor programming terms, a shift register can be thought of as a special case of a queue. In this implementation, each element of  $\mathbb A$  is used multiple times in different parts of the computation. The key characteristic of a shift register is that every element of  $\mathbb A$  can be accessed on every clock cycle. In addition, moving all data items to the next adjacent storage container requires only one clock cycle.

#### **FIFO**

A FIFO can be thought of as a queue with a single point of entry and a single point of exit. This kind of structure is typically used to transmit data between program loops or functions. There is no addressing logic involved, and the implementation details are completely handled by the HLS compiler.

#### **BRAM**

A BRAM is a random-access memory that is embedded into the FPGA fabric. A Xilinx FPGA device includes many of these embedded memories. The exact number of memories is device specific. In processor programming terms, this kind of memory can be thought of as a cache with the following limitations:

- Does not implement cache coherency, collision, and cache miss tracking logic typically found in a processor cache.

- Holds its values only as long as the device is powered on.

- Supports parallel same cycle access to two different memory locations.

# Vivado High-Level Synthesis

## **Overview**

The Xilinx® Vivado® High-Level Synthesis (HLS) compiler provides a programming environment similar to those available for application development on both standard and specialized processors. HLS shares key technology with processor compilers for the interpretation, analysis, and optimization of C/C++ programs. The main difference is in the execution target of the application.

By targeting an FPGA as the execution fabric, HLS enables a software engineer to optimize code for throughout, power, and latency without the need to address the performance bottleneck of a single memory space and limited computational resources. This allows the implementation of computationally intensive software algorithms into actual products, not just functionality demonstrators. This chapter introduces how the HLS compiler works and how it differs from a traditional software compiler.

Application code targeting the HLS compiler uses the same categories as any processor compiler. HLS analyzes all programs in terms of:

- Operations

- Conditional statements

- Loops

- Functions

**IMPORTANT:** HLS can compile almost any C/C++ program. The only coding limitation for HLS is with dynamic language constructs typical in processors with a single memory space. When using HLS, the main dynamic constructs to consider are memory allocation and pointers as described in this chapter.

# **Operations**

Operations refer to both the arithmetic and logical components of an application that are involved in computing a result value. This definition intentionally excludes comparison statements, because these are handled in Conditional Statements.

When working with operations, the main difference between HLS and other compilers is in the restrictions placed on the designer. With a processor compiler, the fixed processing architecture means that the user can only affect performance by limiting operation dependency and manipulating memory layout to maximize cache performance. In contrast, HLS is not constrained by a fixed processing platform and builds an algorithm-specific platform based on user input. This allows an HLS designer to affect application performance in terms of throughput, latency, and power as shown in the examples in this section.

Figure 4-1 shows a set of three operations involved in the computation of result F[i].

```

A[i] = B[i] * C[i];

D[i] = B[i] * E[i];

F[i] = A[i] + D[i];

```

Figure 4-1: Example Code for Three Operations

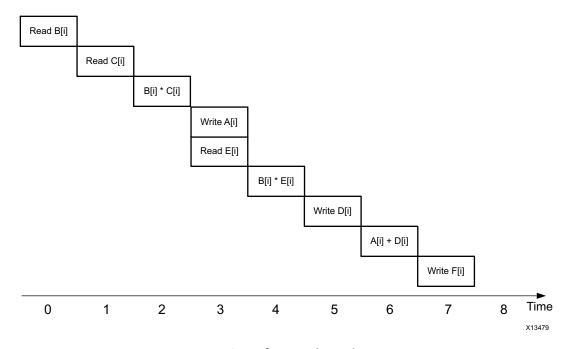

Using a processor, the resulting execution profile is similar to Figure 4-2. This application profile focuses only on the EXE stage of instruction processing in a central processing unit (CPU). This is the only stage in instruction processing that is shared between processors and FPGAs. In this example, the execution trace is sequential due to the execution platform, not the algorithm. Based on the algorithm, the values of A[i] and D[i] can be computed in any order or at the same time. The only algorithmic restriction is that both of these values must be computed before F[i].

Figure 4-2: Execution of Example Code on a Processor

Figure 4-3 shows the result of compiling the code in Figure 4-1 to an FPGA using the default settings in HLS. The resulting execution profile is similar to that of the processor in that the multiplications and addition occur in sequential order. The reason for this default behavior is to minimize the number of building blocks required to implement the user application. Although an FPGA does not have a fixed processing architecture, each device has a maximum number of building blocks it can sustain. Therefore, the designer can evaluate FPGA resources versus application performance versus the number of applications per device.

Figure 4-3: Default Execution of HLS Code on an FPGA

Even with the default behavior, the HLS implementation outperforms the processor execution due to the custom memory architecture created for the algorithm. On the processor, arrays A, B, C, D, E, and F are stored in a single memory space and can only be accessed one at a time. In contrast, HLS detects these memories and creates an independent memory bank for each array, which results in an overlap between the read operations of array B and array C.

The scheduling of the read operation of array  $\mathbb{E}$  in clock cycle 1 shows one of the automatic resource optimizations from HLS. For memory operations, HLS analyzes the banks containing the data and where the value is consumed during computation. Although the read of array  $\mathbb{E}$  can occur during clock cycle 0, HLS automatically places the memory operation as close as possible to the location where the data is consumed to reduce the amount temporary data storage in the circuit. Because the multiplier using the value of  $\mathbb{E}$  does not run until clock cycle 2, there is no benefit in scheduling the read access to occur sooner than clock cycle 1.

Another way in which HLS helps the user control the size of the generated circuit is by providing data types for the sizing of variables. Similar to all compilers, HLS offers the user access to integer, single precision, and double precision data types. This enables rapid migration of software onto the FPGA but might mask algorithm inefficiencies, which are a result of the 32-bit and 64-bit datapaths available in processors.

For example, assume that the code in Figure 4-1 only requires 20-bit values in arrays B, C, and E. In the original processor code, these bit sizes would require arrays A, D, and F to be capable of storing 64-bit values to avoid any loss of precision. HLS can compile the code as is, but this results in an inefficient 64-bit datapath that consumes more resources than is required by the algorithm.

Figure 4-4 shows an example of how to rewrite the code in Figure 4-1 with the HLS arbitrary precision data types. The use of these data types enables rapid software-level exploration and validation of the minimum required precision needed for algorithm correctness. Besides reducing the number of resources required to implement a computation, the use of arbitrary precision data types reduces the number of levels of logic required to complete an operation. This in turn reduces the latency of a design.

```

ap_int<40> A[10], D[10];

ap_int<41> F[10];

ap_int<20> B[10], C[10], E[10];

...

A[i] = B[i] * C[i];

D[i] = B[i] * E[i];

F[i] = A[i] + D[i];

```

Figure 4-4: Coding Example Using HLS Arbitrary Precision Types

As mentioned in Chapter 3, Basic Concepts of Hardware Design, pipelining, or the division of computation into smaller register-bound regions, is an essential FPGA design technique for achieving a target clock frequency. Based on the size of operations, this optimization is automatically implemented by HLS. HLS divides large operators into multiple computation stages with a corresponding increase in circuit latency.

#### **Conditional Statements**

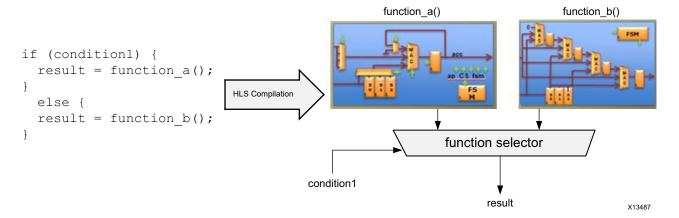

Conditional statements are program control flow statements that are typically implemented as if, if-else, or case statements. These coding structures are an integral part of most algorithms and are fully supported by all compilers, including HLS. The only difference between compilers is how these types of statements are implemented.

With a processor compiler, conditional statements are translated into branch operations that might or might not result in a context switch. The introduction of branches disrupts the maximum instruction execution packing shown in Figure 3-2 by introducing a dependence that affects which instruction is fetched next from memory. This uncertainty results in bubbles in the processor execution pipeline and directly affects program performance.

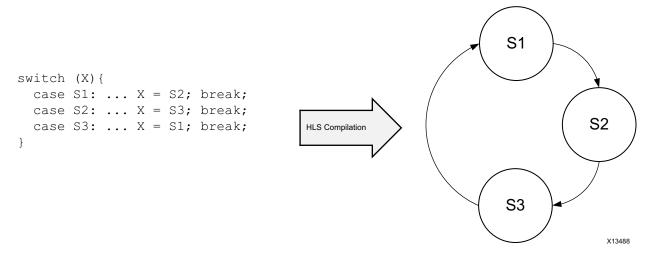

In an FPGA, a conditional statement does not have the same potential impact on performance as in a processor. HLS creates all the circuits described by each branch of the conditional statement. Therefore, the runtime execution of a conditional software statement involves the selection between two possible results rather than a context switch.

## Loops

Loops are a common programming construct for expressing iterative computation. One common misconception is that loops are not supported when working with compilers like HLS. Although this might be true with early versions of compilers for FPGAs, HLS fully supports loops and can even do transformations that are beyond the capabilities of a standard processor compiler. Figure 4-5 shows an example of a simple loop.

```

for(i=0; i < 10; i++)

{

A = A + (B[i] * C[i]);

}</pre>

```

Figure 4-5: Loop Code

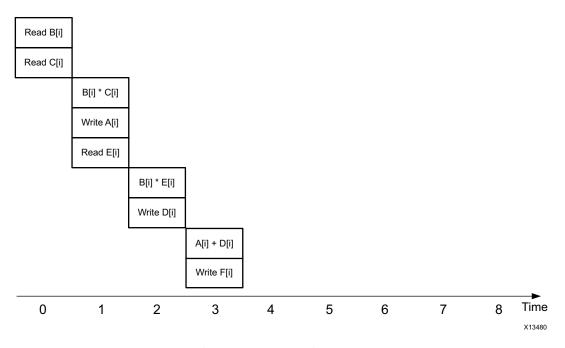

For illustration purposes, assume that the loop takes four clock cycles per iteration regardless of the implementation platform. On a processor, the compiler is forced to schedule loop iterations sequentially for a total run time of 40 cycles, as shown in Figure 4-6.

Figure 4-6: Loop Iteration Scheduling on a Processor

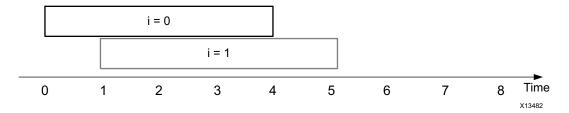

HLS does not have this limitation. Because HLS creates the hardware for the algorithm, it can alter the execution profile of a loop by pipelining iterations. Loop iteration pipelining extends the concept of operation parallelization from within loop iterations to across iterations.

To reduce iteration latency, the first automatic optimization applied by HLS is operator parallelization to the loop iteration body. The second optimization is loop iteration pipelining. This optimization requires user input, because it affects the resource consumption and input data rates of the FPGA implementation.

The default behavior of HLS is to execute loops in the same schedule as a processor, as shown in Figure 4-6. This means that the code in Figure 4-5 has a processing latency of 40 cycles and an input data rate of once every 4 cycles. In this example, the input data rate is defined by how quickly the values of B and C can be sampled from the input.

HLS can parallelize or pipeline the iterations of a loop to reduce computation latency and increase the input data rate. The user controls the level of iteration pipelining by setting the loop initialization interval (II). The II of a loop specifies the number of clock cycles between the start times of consecutive loop iterations. Figure 4-7 shows the resulting loop schedule after setting the value of II to 1.

Figure 4-7: Loop Iteration Scheduling with II = 1

To achieve this result, HLS analyzes the data dependencies and resource contentions between loop iterations 0 and 1 and automatically resolves issues as follows:

- To resolve data dependencies, HLS alters one of the operations in the loop body or gueries the user for algorithm changes.

- To resolve resource contentions, HLS instantiates more copies of the resource or queries the user for algorithm changes.

The effect of loop pipelining on execution characteristics is summarized in Table 4-1.

| ·           |                        |                      |

|-------------|------------------------|----------------------|

| Compiler    | Loop Execution Latency | Input Data Rate      |

| Processor   | 40                     | Every 4 clock cycles |

| Default HLS | 40                     | Every 4 clock cycles |

| HLS, II = 1 | 14                     | Every clock cycle    |

Table 4-1: Loop Execution Profile on Different Compilers

### **Functions**

Functions are a programming hierarchy that can contain operators, loops, and other functions. The treatment of functions in both HLS and processor compilers is similar to that of loops.

In HLS, the main difference between loops and functions is related to terminology. HLS can parallelize the execution of both loops and functions. With loops, this transformation is typically referred to as pipelining, because there is a clear hierarchy difference between operators and loop iterations. With functions, operations outside of a loop body and within loops are in the same hierarchical context, which might lead to confusion if the term pipelining is used. To avoid potential confusion when working with HLS, the parallelization of function call execution is referred to as *dataflow optimization*.

The dataflow optimization instructs HLS to create independent hardware modules for all functions at a given level of program hierarchy. These independent hardware modules are capable of concurrent execution and self-synchronize during data transfer.

## **Dynamic Memory Allocation**

Dynamic memory allocation is one of the memory management techniques available in the C and C++ programming languages. In this method, the user can allocate as much memory as necessary during program runtime. The size of the allocated memory can vary between executions of the program and is allocated from a central physical pool of memory as described in Chapter 3, Basic Concepts of Hardware Design. The function calls typically associated with dynamic memory allocation are shown in Table 4-2.

Table 4-2: Functions Used in Dynamic Memory Management

| С        | C++      |

|----------|----------|

| malloc() | new()    |

| calloc() | delete() |

| free()   |          |

As discussed in Chapter 3, Basic Concepts of Hardware Design, an FPGA does not have a fixed memory architecture onto which the HLS compiler must fit the user application. Instead, HLS synthesizes the memory architecture based on the unique requirements of the algorithm. Therefore, all code provided to the HLS compiler for implementation in an FPGA must use compile time analyzable memory allocation only.

To aid the user in ensuring that all code provided to HLS is synthesizable, the compiler executes a coding compliance pass before analyzing the design. This code compliance pass flags all coding styles that are not suitable for HLS. It is the responsibility of the user to manually change the code and remove all instances of dynamic memory allocation.

The code in Figure 4-8 allocates a region in memory to store 10 values of 32 bits each.

```

int *A = malloc(10*sizeof(int));

```

Figure 4-8: Dynamic Memory Allocation

Although this coding example clearly states a constant memory allocation, the HLS code compliance stage does not analyze the contents of the malloc statement. HLS cannot synthesize code that includes any of the keywords in Table 4-2 even if the allocation is constant, as in the example shown in Figure 4-8. There are two possible methods of modifying this code to comply with HLS. The following code examples show these methods and explain their implications on the FPGA implementation.

The code in Figure 4-9 shows automatic memory allocation by a C/C++ program. HLS implements this memory style in strict accordance with the behavior stipulated by C/C++. This means that the memory created to store array  $\mathbb A$  only stores valid data values during the duration of the function call containing this array. Therefore, the function call is responsible for populating  $\mathbb A$  with valid data before each use.

int A[10];

Figure 4-9: HLS-Compliant Automatic Memory Allocation

The code in Figure 4-10 shows static memory allocation by a C/C++ program. The behavior for this type of memory allocation dictates that the contents of array A are valid across function calls until the program is completely shut down. When working with HLS, the memory that is implemented for array A contains valid data as long as there is power to the circuit.

static int A[10];

Figure 4-10: HLS-Compliant Static Memory Allocation

Both automatic and static memory allocation techniques can increase the overall software memory footprint of an algorithm running on a processor. When specifying algorithms in C/C++ for FPGA implementation, the most important consideration is the overall goal of the user application. That is, the main goal when compiling to an FPGA is not creating the best software algorithm implementation. Instead, when using tools like HLS, the goal is to capture the algorithm in a way that allows the tool to infer the best possible hardware architecture, which results in the best possible implementation.

### **Pointers**

A pointer is an address to a location in memory. Some of the common uses for pointers in a C/C++ program are function parameters, array handling, pointer to pointer, and type casting. The inherent flexibility of this language construct makes it a useful and popular element of C/C++ code. The HLS compiler supports pointer usage that can be completely analyzed at compile time. An analyzable pointer usage is usage that can be fully expressed and computed in a pen and paper computation without the need for runtime information.

The code in Figure 4-8 shows the use of a pointer to reference a dynamically allocated region in memory. As previously described, this usage is not supported with HLS, because the destination address of the pointer is only known during program execution. This does not mean that pointer usage for memory management is unsupported when using the HLS compiler. Figure 4-11 shows a valid coding style in which pointers are used to access a memory.

```

int A[10];

int *pA;

pA = A;

```

Figure 4-11: Managing Array Access with a Pointer

This code is valid, because all uses of pointer pA can be analyzed and mapped back to array A. Because array A is created by automatic memory allocation, HLS can fully determine the properties of A.

Another supported model for memories and pointers is in accessing external memory. When using HLS, any pointer access on function parameters implies either a variable or an external memory. HLS defines an external memory as any memory outside of the scope of the compiler-generated RTL. This means that the memory might be located in another function in the FPGA or in part of an off-chip memory, such as DDR.

In the code shown in Figure 4-12, function foo is a top-level module for HLS with data\_in as a parameter. Based on the multiple pointer access on data\_in, HLS infers that this function parameter is an external memory module, which must be accessed through a bus protocol at the hardware level. A bus protocol, such as Advanced eXtensible Interface (AXI) protocol, specifies how multiple functions can connect and communicate with each other.

```

void foo(int *data_in,...)

{

int item1, item2, item3;

item1 = *data_in;

item2 = *(data_in + 1);

item3 = *(data_in + 2);

...

}

```

Figure 4-12: Pointer to External Memory

# Computation-Centric Algorithms

### **Overview**

Although there is a large body of literature on algorithm analysis, the nuances of computation- versus control-centric algorithms are largely dependent on the implementation platform. This chapter defines computation-centric algorithms in the context of the Vivado® HLS compiler and FPGAs. It also includes examples and best practice recommendations to maximize the performance of the HLS-generated implementation.

A computation-centric algorithm is an algorithm that is configured once per task and cannot change its behavior for the duration of a task. A task in hardware is the same as a function call in a C/C++ program. The size of the task is under the control of the HLS user.

**RECOMMENDED:** In general, it is recommended that the size of a task be based on the natural work division in the algorithm.

Figure 5-1 shows the code for a Sobel edge detection operation. This is an example of a computation-centric algorithm that can be divided into tasks of different sizes. This algorithm is a two-dimensional filtering operation that computes the edge of a region in an image by computing the gradient of each pixel in the x and y directions. As currently written, this code can be compiled by HLS into an FPGA implementation.

```

for(i = 0; i < height; i++) {

for(j = 0; j < width; j++) {

x_dir = 0;

y_dir = 0;

if((i > 0) && (i < (height-1)) && (j > 0) && (j<(width-1))) {

for(rowOffset = -1; rowOffset <= 1; rowOffset++) {

for(colOffset = -1; colOffset <= 1; colOffset++) {

x_dir = x_dir + input_image[i+rowOffset][j+colOffset] * Gx[1+rowOffset][1+colOffset];

y_dir = y_dir + input_image[i+rowOffset][j+colOffset] * Gy[1+rowOffset][1+colOffset];

}

edge_weight = ABS(x_dir) + ABS(y_dir);

output_image[i][j] = edge_weight;

}</pre>

```

Figure 5-1: Sobel Edge Detection Algorithm—Task Choice 1

To properly optimize this algorithm, the designer must first decide the size of a task. The size of a task determines how often the generated hardware module needs to be configured and how often it needs to receive a new batch of data. Figure 5-2 and Figure 5-3 show two possible task definitions for the code in Figure 5-1. An alternate choice is to define the code in Figure 5-1 as a task.

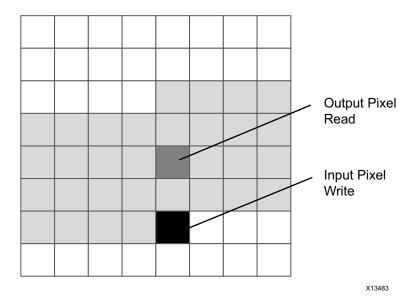

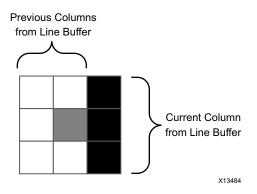

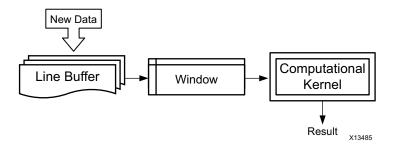

Task Choice 2 (Figure 5-2) creates a hardware module for only the gradient computation. The gradient computation works on a 3x3 pixel window and does not support the concept of a line or an image frame. The problem with this choice is the mismatch between the amount of work executed by this choice and the natural work division of the algorithm. The Sobel edge detection works at the scope of complete images. This means that for this choice of task size, the designer must determine how to partition the image into the 3x3 pixel slices required by the task processor built with HLS. Either a processor or additional hardware modules are needed to complete the functionality of the algorithm.

Figure 5-2: Task Choice 2 for the Sobel Edge Detection Algorithm

Task Choice 3 (Figure 5-3) handles a full pixel line per task. This is an improvement over Task Choice 1, because it requires fewer additional modules to implement the complete functionality of the algorithm. This approach also reduces the interaction with a control processor to once per line. The problem with sizing a task to handle a single line at a time is that the underlying operation requires multiple lines to compute a result. With this choice, a complex control mechanism might be needed to sequence image lines into the HLS-generated hardware module.

```

for(j = 0; j < width; j++){

x_dir = 0;

y_dir = 0;

if((i > 0) && (i < (height-1)) && (j > 0) && (j<(width-1))){