作者 张国斌

在7月19日ARM嵌入式开发设计研讨会上,赛灵思(Xilinx)亚太区业务拓展经理罗霖为与会者带来了《All Programmable SoC Zynq-7000技术及应用》的演讲,在这个演讲中,罗霖分析了赛灵思Zynq-7000器件的优势、生态系统建设现状,并分享了Zynq-7000的应用案例,让与会者了解了Zynq器件在嵌入式应用的优势,引发了大家的浓厚兴趣。

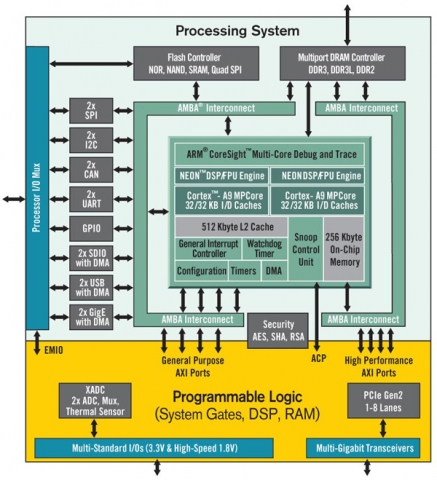

罗霖认为All Programmable SoC是系统集成的一项创新,把设计中普通的分立方案变成了集成方案,不但降低了开发复杂性、成本和功耗,还提升了性能和可靠性,另外Xilinx公司的All Programmable SoC Zynq-7000系列的优势在于软件硬件均可编程,为使用者提供了极大的灵活性。

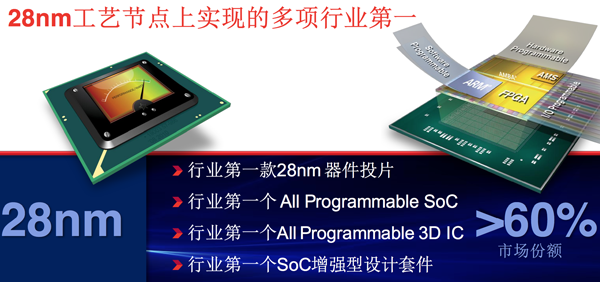

罗霖指出All Programmable SoC Zynq-7000是赛灵思率先将ARM Cortex-A9嵌入FPGA的器件,实际上,除此之外,在28nm工艺节点,赛灵思创造了多项第一。

罗霖表示All programmable SoC和一般SOC不一样地方是可以在芯片上进行二次开发,所以可以满足不同需求,实际上,目前随着嵌入式创新日益成熟,系统客户需要很多个性化的器件,标准器件难以满足用户需求,All programmable SoC可以满足用户的个性化需求。他表示这个器件的价值是可以将以前ARM+DSP的多片方案集成并做扩展。

另外,ARM处理器系统外设是固化好的,方便用户调用,而通过AXI4总线,硬件加速模块还可以访问cache,因此可以带来性能的大幅度提升。

目前能支持这个器件的开发工具很多,这是列举的几个器件。

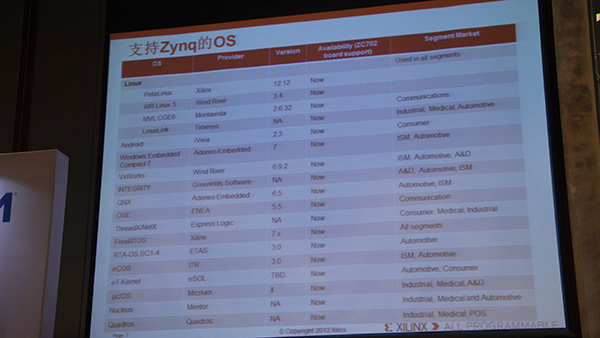

他表示支持Zynq的嵌入式操作系统则更多,我们熟知的多种操作系统如linux,vxworks,android等都支持Znyq,在支持的的OS数量上远超竞争对手同类器件。

Zynq启动流程很简单,以ARM处理器启动

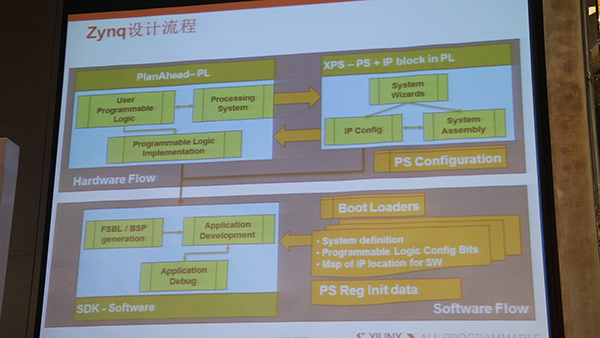

Zynq设计流程很灵活,有多种设计模式如下图所示

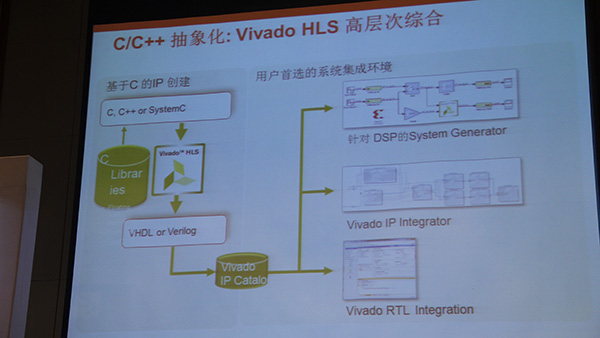

赛灵思主张设计硬件抽象化,就是要把Zynq器件像开发普通ASIC一样开发,让设计师不用去考虑过多底层架构细节,用C语言就可以完成FPGA的开发,这大大降低了FPGA开发的门槛。

支持这个思路的工具就是赛灵思推出的vivado设计套件,它支持高层次综合,可以将C语言转化为支持FPGA开发的HDL语言,并实现对IP的综合和套接,大大方便了开发,罗霖举例说某个通信客户开发通信设备,以前采用DSP开发需要超过一个月的时间,而现在采用Zynq后,仅用一周就开发成功还提升了设备性能。

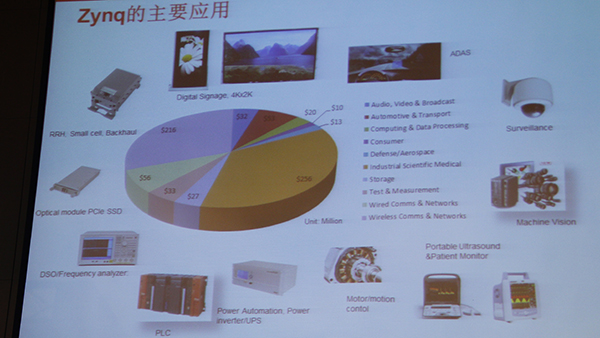

罗霖表示目前Zynq的应用日益拓宽。

这是一个基于Zynq的智能监控案例,它将原来的四片方案简化为一片,并将陈本减少50%!功耗降低50%!而且利用赛灵思的开发工具把开发效率提升了50%!

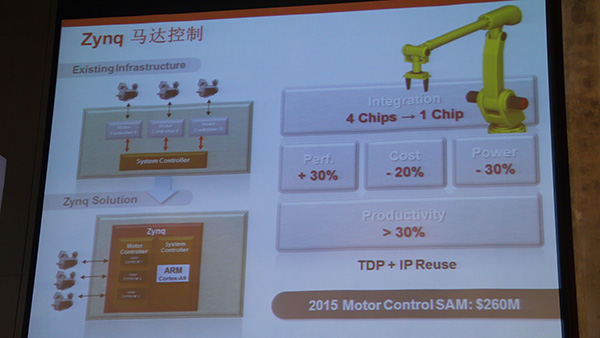

这是一个基于Zynq器件的马达控制案例

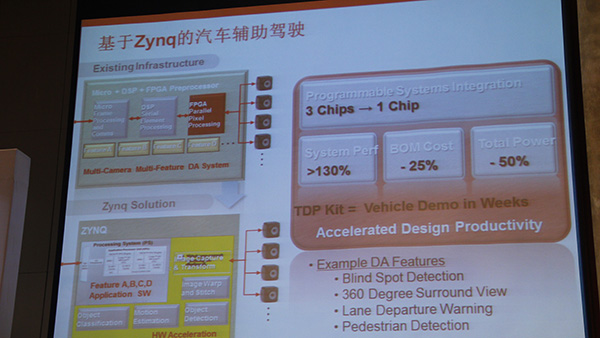

这是一个基于Zynq器件的汽车高级辅助驾驶的案例,可以看到系统性能大大提升同时功耗降低50%

目前支持Zynq器件开发工具很多有赛灵思自己提供的也有合作伙伴安富利zedboard和科通集团的zingboard。

Zynq器件roadmap,未来将向20nm 16nm工艺演进,会嵌入ARM Cortex-A50内核吗?我们拭目以待!

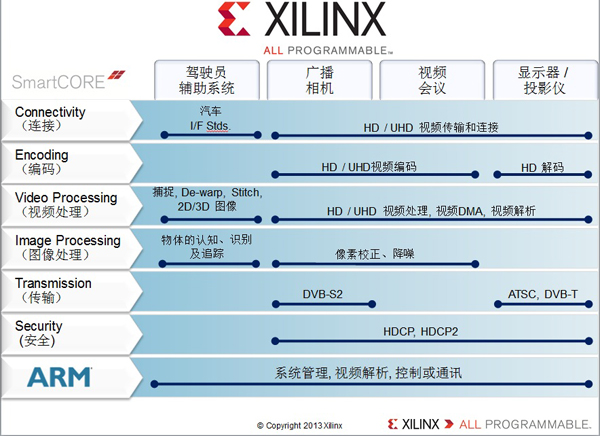

罗霖表示为了进一步降低复杂系统开发难度,赛灵思今年还启动了smarter programmable战略,瞄准通信、数据中心、视频处理和汽车应用。例如智能视频的赛灵思All Programmable Smarter Vision解决方案包括VivadoTM HLS(高层次综合)、最新IP Integrator工具、OpenCV(计算机视觉)库、SmartCORETM IP和专用开发套件。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网